STREAM

About

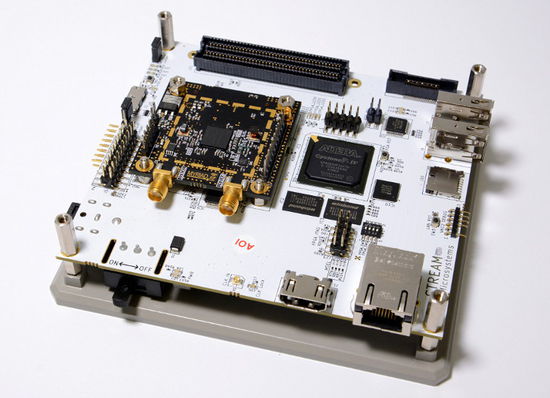

STREAM is a flexible platform for developing high-performance digital and RF designs using an Altera Cyclone IV FPGA and Lime Microsystems FPRF transceiver. The board incorporates SDRAM, Micro SD storage and a selection of other useful peripherals, with expansion via RFDIO and FMC mezzanine cards enabling use with both Myriad-RF 1 and LMS7002M EVB RF modules.

An OpenRISC SoC is available for STREAM that is capable of running Linux and bare metal applications, complete with a peripheral controller for interfacing RFDIO cards such as Myriad-RF 1. This allows for a mixed development model whereby programming and control is done via a flexible RISC processor, with baseband processing taking place directly in the FPGA fabric.

Software is provided for use with the LMS7002M EVB that allows control of the transceiver, ADC spectrum to be analysed via an FFT viewer, and example waveforms to be loaded into the FPGA.

Specifications

FPGA

- Cyclone IV EP4CE40F23C7N device in 484-pin FBGA

- 39’600 LEs

- 1134 Kbits embedded memory

- 116 embedded 18×18 multipliers

- 4 PLLs

- JTAG mode configuration

- Serial mode configuration via Cypress FX3

Memory

- 2x64MB (16bit) SDRAM

- Micro SD with access via USB Host controller

Interfaces

- Micrel KSZ9021GN GbE controller

- Dual USB 2.0 host (VNC2-48L1B)

- Cypress FX3 USB 3.0 (CYUSB3013)

- DVI transmitter (TFP410)

Expansion

- FPGA Mezzanine Card (FMC) LPC connector

- RFDIO (FX80P) high-speed connector

- GPIO header

Programming and debug

- FPGA JTAG header (Altera USB-Blaster)

- Cypress FX3 JTAG header

- Mictor E5346A Agilent test equipment connector

Clock system

- 30.72MHz oscillator

- Programmable clock generator (SI5351C) for the FPGA reference clock input and RF mezzanine boards

- Locking to external clock circuit (ADF4002)

Schematics

-

Block diagram

-

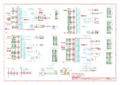

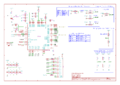

FPGA banks 1-4

-

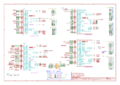

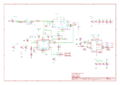

FPGA banks 5-8

-

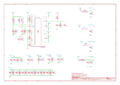

SDRAM

-

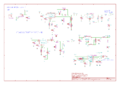

USB 3.0 device (FX3)

-

USB 2.0 host

-

Peripherals

-

Ethernet

-

Clocks

-

USB 3.0 power supply

-

Board power supply 1

-

Board power supply 2

-

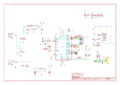

Clocks block diagram

-

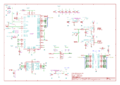

FPGA power distribution

-

FMC and Myriad-RF connectors

Licensing

Hardware

The hardware designs are licensed under a Creative Commons Attribution 3.0 Unported licence.

FPGA design

For details of the FPGA design licensing please see the associated COPYING file(s) in the project's GitHub repository. However, please note that this does not extend to any files provided with the Altera design tools; see the relevant files for the associated terms and conditions.

See Also

- Reference Development Kit

- STREAM Communications

- STREAM OpenRISC

- STREAM Linux Installation

- STREAM Project Page

| |||||||||||||||||||||