LimeSDR-PCIe v1.3 hardware description

Draft

Draft

Introduction

LimeSDR-PCIe is low-cost software defined radio board based on Lime LMS7002M Field Programmable Radio Frequency (FPRF) transceiver and Altera Cyclone IV GX PFGA, through which apps can be programmed to support any type of wireless standard, e.g. UMTS, LTE, LoRa, GPS, WiFi, Zigbee, RFID, Digital Broadcasting, Radar and many more.

Complete Development Kit Package

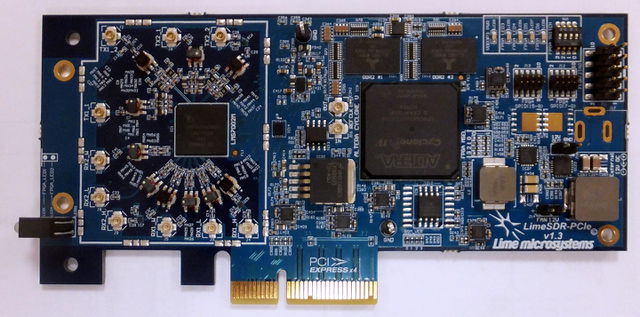

The LimeSDR-PCIe v1.3 board from full package showed in Figure 1.

Development kit content:

- LimeSDR-PCIe v1.3 board

- USB stick containing following files:

- Doc/ - Documentation files for LimeSDR-PCIe

- Drivers/ - Windows drivers for LimeSDR-PCIe

- Gateware/ - FPGA gateware related files for LimeSDR-PCIe v1.3

- Gui/ - LimeSuiteGUI software and related files

LimeSDR-PCIe Board Key Features

The LimeSDR-PCIe development board provides a hardware platform for developing and prototyping high-performance and logic-intensive digital and RF designs using Altera’s Cyclone IV GX FPGA and Lime Microsystems transceiver.

LimeSDR-PCIe board features:

- RF transceiver:

- Lime Microsystems LMS7002M

- FPGA Features

- Cyclone IV GX (EP4CGX30CF23C7N) device in 484-pin FBGA

- 29’440 logic elements

- 1080 Kbits embedded memory

- 80 embedded 18x18 multipliers

- 4 general and 2 multipurpose PLLs

- 4 high-speed transceivers

- PCIe (PIPE) hard IP block

- FPGA Configuration

- JTAG mode configuration

- Active serial mode configuration

- Possibility to update FPGA gateware by using PCIe interface

- Memory Devices

- 2x 1Gbit (64M x 16) dual channel DDR2 SDRAM

- 4Mbit flash for FPGA data

- 64Mbit flash for FPGA gateware

- 128Kb (16K x 8) EEPROM for LMS MCU firmware and 512Kb (64K x 8) LMS MCU data

- Connections

- PCI Express x4 (4 lanes)

- Coaxial RF (U.FL) connectors

- FPGA GPIO 2x8 (3.3V) headers

- FPGA and JTAG connector

- DC (12V) power jack and pinheader

- FAN (12V) connector

- Clock System

- 30.72MHz ±250 ppb onboard VCTCXO

- Possibility to lock VCTCXO to external clock or tune VCTCXO by onboard DAC

- Programmable clock generator for the FPGA reference clock input or LMS PLLs

- 100 MHz and 2x 50MHz crystal oscillators for FPGA

- Board Size 68,9mm x 136,85mm

For more information on the following topics, refer to the respective documents:

- Cyclone IV device family, refer to Cyclone IV Device Handbook [link]

- LMS7002M transceiver resources [link]

LimeSDR-PCIe board overview

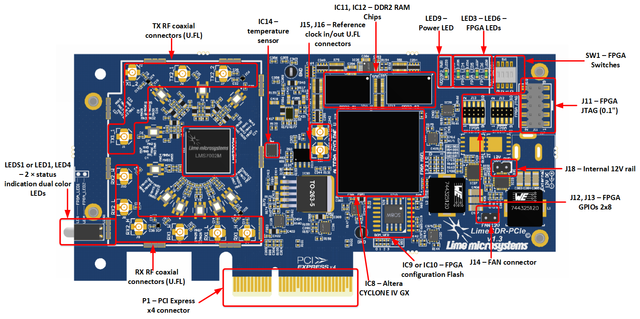

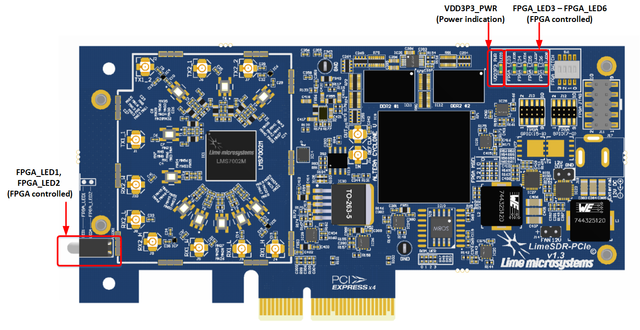

LimeSDR-PCIe board version 1.3 picture with highlighted major connections and components presented in Figure 2 and Figure 3. There are three connector types – data and debugging (PCIe, FPGA GPIO and JTAG), power (DC jack - optional) and high frequency (RF and reference clock). LimeSDR-PCIe board version 1.3 picture with highlighted components on top presented in Figure 2.

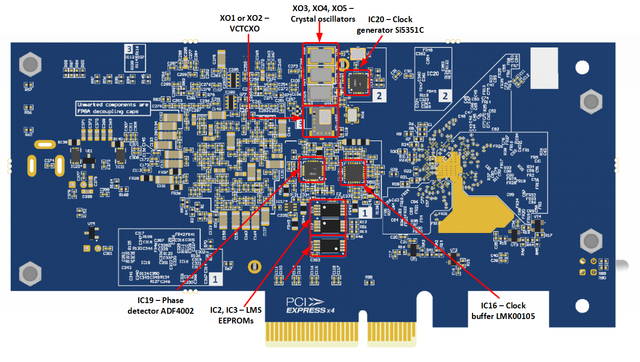

LimeSDR-PCIe board version 1.3 picture with highlighted components on bottom presented in Figure 3

Board components description listed in the Table 1.

| Featured Devices | ||

|---|---|---|

| Board reference | Type | Description |

| IC1 | FPRF | Field programmable RF transceiver LMS7002M |

| IC8 | FPGA | Altera Cyclone IV GX (EP4CGX30CF23C7N) device in 484-pin FBGA |

| Miscellaneous devices onboard | ||

| IC14 | IC | Temperature sensor LM75 |

| IC4, IC5, IC6, IC7 | IC | SPDT Switch |

| Configuration, Status and Setup Elements | ||

| J11 | JTAG chain pinheader | FPGA programming pinheader for Altera USB-Blaster download cable, 0.1” pitch |

| LEDS1 or LED1, LED4 | Red-green status LEDs | User defined FPGA indication dual colour (red – green) LEDs. LEDS1 if two TH LEDs with standoff or two SMD LEDs are populated. |

| LED5-LED8 | Green status LEDs | User defined FPGA indication green LEDs (LED3-LED6). |

| LED9 | Green status LEDs | Power indication |

| General User Input/Output | ||

| J12, J13 | Pinheader | 8 + 8 FPGA GPIOs, 0.05” pitch |

| J14 | Pinheader | 12V fan connection pinheader, 0.1” pitch |

| J18 | Pinheader | 12V internal power rail. Can be used to power external devices. |

| SW1 | Switch | 4 pole switch |

| Memory Devices | ||

| Board Reference | Type | Description |

| IC11, IC12 | DDR2 memory | 1Gbit (64M x 16) DDR2 SDRAM with a 16-bit data bus |

| IC2, IC3 | EEPROM | 128K (16K x 8) and 512K (64K x 8) EEPROMs for LMS7002 MCU firmware and data |

| IC15 | EEPROM | 128K (16K x 8) EEPROM for FPGA data |

| IC9, IC10 | Flash memory | 64Mbit Flash for FPGA configuration (only one is soldered). |

| Communication Ports | ||

| P1 | PCIe connector | PCI Express x4 connector |

| Clock Circuitry | ||

| XO1, XO2, XO3 | VCTCXO | Voltage Controlled, Temperature Compensated Crystal Oscillator (30.72MHz, only one is soldered). |

| IC19 | IC | Programmable clock generator (Si5351C) for the FPGA reference clock input and RF boards |

| IC18 | IC | Phase detector (ADF4002) |

| J15 | U.FL connector | RF connector for reference clock output |

| J16 | U.FL connector | RF connector for external reference clock input |

| IC17 | IC | DAC for TCXO (XO1 or XO2) frequency tuning |

| Power Supply | ||

| J17 | DC input jack | External 12V DC power supply (Optional) |

| J18 | Pinheader | External 12V DC power supply and internal main power rail |

LMS7002M based connectivity

All LMS7002M RF transceiver signals are connected to FPGA Bank 8 (power rail: VDIO_LMS_FPGA; voltage: 2.5V-default or 3.3V). The interface and control signals are described below:

- Digital Interface Signals: LMS7002 is using data bus LMS_DIQ1_D[11:0] and LMS_DIQ2_D[11:0], LMS_ENABLE_IQSEL1 and LMS_ENABLE_IQSEL2, LMS_FCLK1 and LMS_FCLK2, LMS_MCLK1 and LMS_MCLK2 signals to transfer data to/from FPGA. Indexes 1 and 2 indicate transceiver digital data PORT-1 or PORT-2. Any of these ports can be used to transmit or receive data. By default PORT-1 is selected as transmit port and PORT-2 is selected as receiver port. The FCLK# is input clock and MCLK# is output clock for LMS7002M transceiver. TXNRX signals sets ports directions. For LMS7002M interface timing details refer to LMS7002M transceiver datasheet page 12-13. [link].

- SPI Interface: LMS7002M transceiver is configured via 4-wire SPI interface; FPGA_SPI0_SCLK, FPGA_SPI0_MOSI, FPGA_SPI0_MISO, FPGA_SPI0_LMS_SS.

- I2C Interface: used access EEPROM memories for LMS7002M MCU firmware and data. I2C interface is using LMS_I2C_SCL, LMS_I2C_SDA signals.

- Control Signals: these signals are used for optional functionality:

- LMS_RXEN, LMS_TXEN – receiver and transmitter enable/disable signals.

- LMS_RESET – LMS7002M reset.

| Chip pin (IC1) | Chip reference (IC1) | Schematic signal name | FPGA pin | FPGA I/O standard | Comment |

|---|---|---|---|---|---|

| AM24 | xoscin_rx | RxPLL_CLK | - | 2.5V (3.3V) | Connected to 30.72 MHz clock |

| E5 | xoscin_tx | TxPLL_CLK | - | 2.5V (3.3V) | Connected to 30.72 MHz clock |

| E27 | RESET | LMS_RESET | A1 | 2.5V (3.3V) | |

| U29 | TXEN | LMS_TXEN | A7 | 2.5V (3.3V) | |

| D28 | SEN | FPGA_SPI0_LMS_SS | B1 | 2.5V (3.3V) | SPI interface |

| C29 | SCLK | FPGA_SPI0_SCLK | B3 | 2.5V (3.3V) | SPI interface |

| F30 | SDIO | FPGA_SPI0_MOSI | C1 | 2.5V (3.3V) | SPI interface |

| F28 | SDO | FPGA_SPI0_MISO | A3 | 2.5V (3.3V) | SPI interface |

| D26 | SDA | LMS_I2C_SDA | A2 (via R46) | 2.5V (3.3V) | Connected to EEPROMS |

| C27 | SCL | LMS_I2C_SCL | G11 (via R51) | 2.5V (3.3V) | Connected to EEPROMS |

| AB34 | MCLK1 | LMS_MCLK1 | K10 | 2.5V (3.3V) | |

| AA33 | FCLK1 | LMS_FCLK1 | H9 | 2.5V (3.3V) | |

| V32 | TXNRX1 | LMS_TXNRX1 | C3 | 2.5V (3.3V) | |

| V34 | RXEN | LMS_RXEN | C2 | 2.5V (3.3V) | |

| Y32 | ENABLE_IQSEL1 | LMS_ENABLE_IQSEL1 | D6 | 2.5V (3.3V) | |

| AG31 | DIQ1_D0 | LMS_DIQ1_D0 | D9 | 2.5V (3.3V) | |

| AF30 | DIQ1_D1 | LMS_DIQ1_D1 | B7 | 2.5V (3.3V) | |

| AF34 | DIQ1_D2 | LMS_DIQ1_D2 | H8 | 2.5V (3.3V) | |

| AE31 | DIQ1_D3 | LMS_DIQ1_D3 | C8 | 2.5V (3.3V) | |

| AD30 | DIQ1_D4 | LMS_DIQ1_D4 | C7 | 2.5V (3.3V) | |

| AC29 | DIQ1_D5 | LMS_DIQ1_D5 | C9 | 2.5V (3.3V) | |

| AE33 | DIQ1_D6 | LMS_DIQ1_D6 | H7 | 2.5V (3.3V) | |

| AD32 | DIQ1_D7 | LMS_DIQ1_D7 | G8 | 2.5V (3.3V) | |

| AC31 | DIQ1_D8 | LMS_DIQ1_D8 | E8 | 2.5V (3.3V) | |

| AC33 | DIQ1_D9 | LMS_DIQ1_D9 | G7 | 2.5V (3.3V) | |

| AB30 | DIQ1_D10 | LMS_DIQ1_D10 | F8 | 2.5V (3.3V) | |

| AB32 | DIQ1_D11 | LMS_DIQ1_D11 | E6 | 2.5V (3.3V) | |

| U33 | CORE_LDO_EN | LMS_CORE_LDO_EN | C4 | 2.5V (3.3V) | |

| P34 | MCLK2 | LMS_MCLK2 | M11 | 2.5V (3.3V) | |

| R29 | FCLK2 | LMS_FCLK2 | C5 | 2.5V (3.3V) | |

| U31 | TXNRX2 | LMS_TXNRX2 | A4 | 2.5V (3.3V) | |

| R33 | ENABLE_IQSEL2 | LMS_ENABLE_IQSEL2 | B6 | 2.5V (3.3V) | |

| H30 | DIQ2_D0 | LMS_DIQ2_D0 | G6 | 2.5V (3.3V) | |

| J31 | DIQ2_D1 | LMS_DIQ2_D1 | E5 | 2.5V (3.3V) | |

| K30 | DIQ2_D2 | LMS_DIQ2_D2 | A8 | 2.5V (3.3V) | |

| K32 | DIQ2_D3 | LMS_DIQ2_D3 | D7 | 2.5V (3.3V) | |

| L31 | DIQ2_D4 | LMS_DIQ2_D4 | D8 | 2.5V (3.3V) | |

| K34 | DIQ2_D5 | LMS_DIQ2_D5 | F6 | 2.5V (3.3V) | |

| M30 | DIQ2_D6 | LMS_DIQ2_D6 | C6 | 2.5V (3.3V) | |

| M32 | DIQ2_D7 | LMS_DIQ2_D7 | D4 | 2.5V (3.3V) | |

| N31 | DIQ2_D8 | LMS_DIQ2_D8 | A5 | 2.5V (3.3V) | |

| N33 | DIQ2_D9 | LMS_DIQ2_D9 | D5 | 2.5V (3.3V) | |

| P30 | DIQ2_D10 | LMS_DIQ2_D10 | B4 | 2.5V (3.3V) | |

| P32 | DIQ2_D11 | LMS_DIQ2_D11 | A6 | 2.5V (3.3V) |

PCI Express connector

For data transfer LimeSDR–PCIe board has PCI express connector with four lanes. PCI express interface is implemented in FPGA. Pin connection and corresponding signal names are listed in Table 3.

| Connector pin | Schematic signal name | FPGA pin | I/O standard | Comment |

|---|---|---|---|---|

| B5 | PCIE_SMCLK | A10 | 3.3V | |

| B6 | PCIE_SMDAT | B10 | 3.3V | |

| B11 | PCIE_WAKEn | G12 | 3.3V | Signal is disconnected with not fitted R100 resistor |

| B14 | PCIE_HSO0_P | Y2 | 1.5-V PCML | |

| B15 | PCIE_HSO0_N | Y1 | 1.5-V PCML | |

| B19 | PCIE_HSO1_P | T2 | 1.5-V PCML | |

| B20 | PCIE_HSO1_N | T1 | 1.5-V PCML | |

| B23 | PCIE_HSO2_P | M2 | 1.5-V PCML | |

| B24 | PCIE_HSO2_N | M1 | 1.5-V PCML | |

| B27 | PCIE_HSO3_P | H2 | 1.5-V PCML | |

| B28 | PCIE_HSO3_N | H1 | 1.5-V PCML | |

| A11 | PCIE_PERSTn | H12 | 3.3V | |

| A13 | PCIE_REFCLK_P | M7 | HCSL | |

| A14 | PCIE_REFCLK_N | N7 | HCSL | |

| A16 | PCIE_HSI0_P | V2 | 1.5-V PCML | AC coupled |

| A17 | PCIE_HSI0_N | V1 | 1.5-V PCML | AC coupled |

| A21 | PCIE_HSI1_P | P2 | 1.5-V PCML | AC coupled |

| A22 | PCIE_HSI1_N | P1 | 1.5-V PCML | AC coupled |

| A25 | PCIE_HSI2_P | K2 | 1.5-V PCML | AC coupled |

| A26 | PCIE_HSI2_N | K1 | 1.5-V PCML | AC coupled |

| A29 | PCIE_HSI3_P | F2 | 1.5-V PCML | AC coupled |

| A30 | PCIE_HSI3_N | F1 | 1.5-V PCML | AC coupled |

SDRAM

LimeSDR-PCIe board has two 128MB (16bit bus) DDR2 SDRAM ICs (AS4C64M16D2-25BCN [link]) connected to double data rate pins on Cyclone IV GX 1.8V Bank 3, 4 and 5. RAM chips (IC11, IC12) are connected to separate memory controllers so RAM chips works in dual channel mode. The memory can be used for data manipulation at high data rates between transceiver and FPGA. Pin connection and corresponding signal names are listed in Table 5 and Table 6.

| RAM reference | RAM pin | Schematic signal name | FPGA pin | FPGA I/O standard | Comments |

|---|---|---|---|---|---|

| A0 | M8 | DDR2_1_A0 | W20 | SSTL-18 Class I | Active termination |

| A1 | M3 | DDR2_1_A1 | AA19 | SSTL-18 Class I | Active termination |

| A2 | M7 | DDR2_1_A2 | AA21 | SSTL-18 Class I | Active termination |

| A3 | N2 | DDR2_1_A3 | AB19 | SSTL-18 Class I | Active termination |

| A4 | N8 | DDR2_1_A4 | V21 | SSTL-18 Class I | Active termination |

| A5 | N3 | DDR2_1_A5 | AB20 | SSTL-18 Class I | Active termination |

| A6 | N7 | DDR2_1_A6 | W22 | SSTL-18 Class I | Active termination |

| A7 | P2 | DDR2_1_A7 | AA20 | SSTL-18 Class I | Active termination |

| A8 | P8 | DDR2_1_A8 | V22 | SSTL-18 Class I | Active termination |

| A9 | P3 | DDR2_1_A9 | AB21 | SSTL-18 Class I | Active termination |

| A10 | M2 | DDR2_1_A10 | AB17 | SSTL-18 Class I | Active termination |

| A11 | P7 | DDR2_1_A11 | U22 | SSTL-18 Class I | Active termination |

| A12 | R2 | DDR2_1_A12 | Y22 | SSTL-18 Class I | Active termination |

| DQ0 | G8 | DDR2_1_DQ0 | AB10 | SSTL-18 Class I | |

| DQ1 | G2 | DDR2_1_DQ1 | AB14 | SSTL-18 Class I | |

| DQ2 | H7 | DDR2_1_DQ2 | AB15 | SSTL-18 Class I | |

| DQ3 | H3 | DDR2_1_DQ3 | Y13 | SSTL-18 Class I | |

| DQ4 | H1 | DDR2_1_DQ4 | Y14 | SSTL-18 Class I | |

| DQ5 | H9 | DDR2_1_DQ5 | W13 | SSTL-18 Class I | |

| DQ6 | F1 | DDR2_1_DQ6 | W14 | SSTL-18 Class I | |

| DQ7 | F9 | DDR2_1_DQ7 | W15 | SSTL-18 Class I | |

| DQ8 | C8 | DDR2_1_DQ8 | AB18 | SSTL-18 Class I | |

| DQ9 | C2 | DDR2_1_DQ9 | AA16 | SSTL-18 Class I | |

| DQ10 | D7 | DDR2_1_DQ10 | AA18 | SSTL-18 Class I | |

| DQ11 | D3 | DDR2_1_DQ11 | Y15 | SSTL-18 Class I | |

| DQ12 | D1 | DDR2_1_DQ12 | Y16 | SSTL-18 Class I | |

| DQ13 | D9 | DDR2_1_DQ13 | Y18 | SSTL-18 Class I | |

| DQ14 | B1 | DDR2_1_DQ14 | Y19 | SSTL-18 Class I | |

| DQ15 | B9 | DDR2_1_DQ15 | W17 | SSTL-18 Class I | |

| BA0 | L2 | DDR2_1_BA0 | T20 | SSTL-18 Class I | Active termination |

| BA1 | L3 | DDR2_1_BA1 | R20 | SSTL-18 Class I | Active termination |

| BA2 | L1 | DDR2_1_BA2 | U20 | SSTL-18 Class I | Active termination |

| CKE | K2 | DDR2_1_CKE | T19 | SSTL-18 Class I | Active termination |

| CK | J8 | DDR2_1_CK_P | R9 | SSTL-18 Class I | Termination resistor R73 |

| CK# | K8 | DDR2_1_CK_N | T9 | SSTL-18 Class I | Termination resistor R73 |

| WE# | K3 | DDR2_1_WEn | V20 | SSTL-18 Class I | Active termination |

| CAS# | L7 | DDR2_1_CASn | P22 | SSTL-18 Class I | Active termination |

| RAS# | K7 | DDR2_1_RASn | T21 | SSTL-18 Class I | Active termination |

| CS# | L8 | DDR2_1_CSn | T22 | SSTL-18 Class I | Active termination |

| ODT | K9 | DDR2_1_ODT | R21 | SSTL-18 Class I | Active termination |

| LDM | F3 | DDR2_1_DM0 | R13 | SSTL-18 Class I | |

| UDM | B3 | DDR2_1_DM1 | U15 | SSTL-18 Class I | |

| LDQS | F7 | DDR2_1_DQS0 | T13 | SSTL-18 Class I | |

| LDQS# | E8 | DDR2_1_DQS0n | - | To GND via R76 | |

| UDQS | B7 | DDR2_1_DQS1 | AA15 | SSTL-18 Class I | |

| UDQS# | A8 | DDR2_1_DQS1n | - | To GND via R77 | |

| VREF | J2 | VREF_DDR2 | IC8 Banks 3, 4, 5 VREF |

| RAM reference | RAM pin | Schematic signal name | FPGA pin | FPGA I/O standard | Comments |

|---|---|---|---|---|---|

| A0 | M8 | DDR2_2_A0 | M13 | SSTL-18 Class I | Active termination |

| A1 | M3 | DDR2_2_A1 | P14 | SSTL-18 Class I | Active termination |

| A2 | M7 | DDR2_2_A2 | M14 | SSTL-18 Class I | Active termination |

| A3 | N2 | DDR2_2_A3 | T11 | SSTL-18 Class I | Active termination |

| A4 | N8 | DDR2_2_A4 | N13 | SSTL-18 Class I | Active termination |

| A5 | N3 | DDR2_2_A5 | N15 | SSTL-18 Class I | Active termination |

| A6 | N7 | DDR2_2_A6 | M15 | SSTL-18 Class I | Active termination |

| A7 | P2 | DDR2_2_A7 | M16 | SSTL-18 Class I | Active termination |

| A8 | P8 | DDR2_2_A8 | P13 | SSTL-18 Class I | Active termination |

| A9 | P3 | DDR2_2_A9 | P15 | SSTL-18 Class I | Active termination |

| A10 | M2 | DDR2_2_A10 | R15 | SSTL-18 Class I | Active termination |

| A11 | P7 | DDR2_2_A11 | N14 | SSTL-18 Class I | Active termination |

| A12 | R2 | DDR2_2_A12 | N17 | SSTL-18 Class I | Active termination |

| DQ0 | G8 | DDR2_2_DQ0 | AB4 | SSTL-18 Class I | |

| DQ1 | G2 | DDR2_2_DQ1 | AB5 | SSTL-18 Class I | |

| DQ2 | H7 | DDR2_2_DQ2 | AA6 | SSTL-18 Class I | |

| DQ3 | H3 | DDR2_2_DQ3 | Y5 | SSTL-18 Class I | |

| DQ4 | H1 | DDR2_2_DQ4 | Y6 | SSTL-18 Class I | |

| DQ5 | H9 | DDR2_2_DQ5 | Y7 | SSTL-18 Class I | |

| DQ6 | F1 | DDR2_2_DQ6 | W5 | SSTL-18 Class I | |

| DQ7 | F9 | DDR2_2_DQ7 | W6 | SSTL-18 Class I | |

| DQ8 | C8 | DDR2_2_DQ8 | AB6 | SSTL-18 Class I | |

| DQ9 | C2 | DDR2_2_DQ9 | W9 | SSTL-18 Class I | |

| DQ10 | D7 | DDR2_2_DQ10 | Y9 | SSTL-18 Class I | |

| DQ11 | D3 | DDR2_2_DQ11 | AA9 | SSTL-18 Class I | |

| DQ12 | D1 | DDR2_2_DQ12 | AB8 | SSTL-18 Class I | |

| DQ13 | D9 | DDR2_2_DQ13 | W11 | SSTL-18 Class I | |

| DQ14 | B1 | DDR2_2_DQ14 | Y11 | SSTL-18 Class I | |

| DQ15 | B9 | DDR2_2_DQ15 | AA10 | SSTL-18 Class I | |

| BA0 | L2 | DDR2_2_BA0 | AB13 | SSTL-18 Class I | Active termination |

| BA1 | L3 | DDR2_2_BA1 | AA13 | SSTL-18 Class I | Active termination |

| BA2 | L1 | DDR2_2_BA2 | AA4 | SSTL-18 Class I | Active termination |

| CKE | K2 | DDR2_2_CKE | T14 | SSTL-18 Class I | Active termination |

| CK | J8 | DDR2_2_CK_P | W4 | SSTL-18 Class I | Termination resistor R79 |

| CK# | K8 | DDR2_2_CK_N | Y4 | SSTL-18 Class I | Termination resistor R79 |

| WE# | K3 | DDR2_2_WEn | T15 | SSTL-18 Class I | Active termination |

| CAS# | L7 | DDR2_2_CASn | R19 | SSTL-18 Class I | Active termination |

| RAS# | K7 | DDR2_2_RASn | U14 | SSTL-18 Class I | Active termination |

| CS# | L8 | DDR2_2_CSn | AB11 | SSTL-18 Class I | Active termination |

| ODT | K9 | DDR2_2_ODT | W18 | SSTL-18 Class I | Active termination |

| LDM | F3 | DDR2_2_DM0 | W7 | SSTL-18 Class I | |

| UDM | B3 | DDR2_2_DM1 | W12 | SSTL-18 Class I | |

| LDQS | F7 | DDR2_2_DQS0 | Y8 | SSTL-18 Class I | |

| LDQS# | E8 | DDR2_2_DQS0n | - | To GND via R82 | |

| UDQS | B7 | DDR2_2_DQS1 | Y10 | SSTL-18 Class I | |

| UDQS# | A8 | DDR2_2_DQS1n | - | To GND via R83 | |

| VREF | J2 | VREF_DDR2 | IC8 Banks 3, 4, 5 VREF |

Low speed interfaces

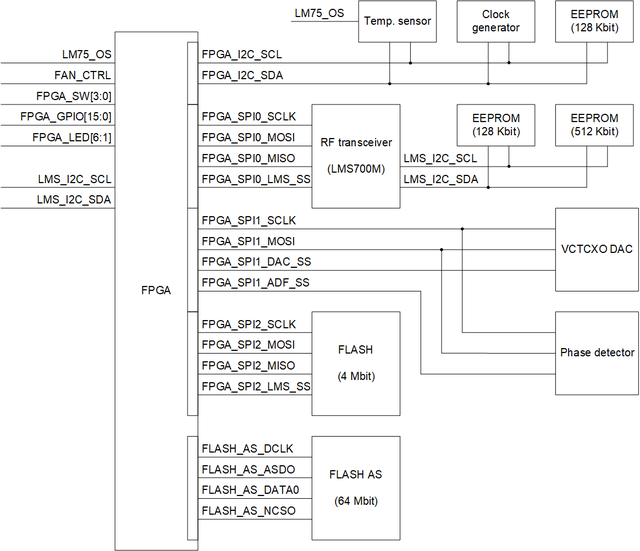

LimeSDR-PCIe board low speed interfaces is presented in Figure 4. More detailed information is provided in the following sections.

Indication LEDs

LimeSDR-PCIe board comes with 6 indication LEDs which can be controlled from FPGA. By default, two of them (FPGA_LED1 and FPGA_LED2) are trough-hole dual colour LEDs and are mounted on the back edge of the board using right-angle plastic holder. The remaining four LEDs (FPGA_LED3 to FPGA_LED6) are SMD single green colour LEDs. There is one SMD single green colour LED named VDD3P3_PWR which is hardwired to VCC3P3 power rail and lit up whenever the board is powered on.

| Board label | Schematic reference | Colour | Schematic signal name | FPGA pin | I/O standard | Comment |

|---|---|---|---|---|---|---|

| FPGA_LED1 | LEDS1 (LED1) | Red/green | FPGA_LED1_R | E20 | 3.3V | LEDS1 - trough-hole

LED1 - optional SMD |

| FPGA_LED1_G | H21 | 3.3V | ||||

| FPGA_LED2 | LEDS1 (LED4) | Red/green | FPGA_LED2_R | G21 | 3.3V | LEDS1 - trough-hole

LED4 - optional SMD |

| FPGA_LED2_G | G20 | 3.3V | ||||

| FPGA_LED3 | LED5 | Green | FPGA_LED3 | K20 | 3.3V | |

| FPGA_LED4 | LED6 | Green | FPGA_LED4 | K19 | 3.3V | |

| FPGA_LED5 | LED7 | Green | FPGA_LED5 | K22 | 3.3V | |

| FPGA_LED6 | LED8 | Green | FPGA_LED6 | H20 | 3.3V | |

| VDD3P3_PWR | LED9 | Green | - | - | Power LED |

SPI interfaces

LimeSDR-PCIe board has four SPI interfaces with their own slave devices:

- Flash for FPGA gateware: Flash memory (IC9 or IC10) is used to store FPGA gateware.

| Schematic signal name | FPGA pin | I/O standard | Comment |

|---|---|---|---|

| FPGA_AS_DCLK | D3 | 3.3V | |

| FPGA_AS_ASDO | D1 | 3.3V | |

| FPGA_AS_DATA0 | K4 | 3.3V | |

| FPGA_AS_NCSO | J4 | 3.3V | SPI flash slave select |

- RFIC: RFIC is connected to FPGA_SPI0.

| Schematic signal name | FPGA pin | I/O standard | Comment |

|---|---|---|---|

| FPGA_SPI0_SCLK | B3 | 2.5V (3.3V) | |

| FPGA_SPI0_MOSI | C1 | 2.5V (3.3V) | |

| FPGA_SPI0_MISO | A3 | 2.5V (3.3V) | |

| FPGA_SPI0_LMS_SS | B1 | 2.5V (3.3V) | IC1 (LMS7002) SPI slave select |

- Phase detector and DAC: phase detector with VCTCXO DAC are connected to FPGA_SPI1.

| Schematic signal name | FPGA pin | I/O standard | Comment |

|---|---|---|---|

| FPGA_SPI0_SCLK | B3 | 2.5V (3.3V) | |

| FPGA_SPI0_MOSI | C1 | 2.5V (3.3V) | |

| FPGA_SPI0_MISO | A3 | 2.5V (3.3V) | |

| FPGA_SPI0_LMS_SS | B1 | 2.5V (3.3V) | IC1 (LMS7002) SPI slave select |

- Flash memory: flash memory is connected to FPGA_SPI2.

| Schematic signal name | FPGA pin | I/O standard | Comment |

|---|---|---|---|

| FPGA_SPI2_SCLK | J19 | 3.3V | |

| FPGA_SPI2_MOSI | H22 | 3.3V | |

| FPGA_SPI2_MISO | J21 | 3.3V | |

| FPGA_SPI2_FLASH_SS | J22 | 3.3V | FPGA flash (IC13) slave select |

I2C interfaces

Board has two independent I2C interfaces: FPGA_I2C and LMS_I2C.

- FPGA_I2C: this interface has several slave devices temperature sensor, EEPROM and clock generator. Information for slave devices are provided in Table 12, signal connectivity information is in Table 13.

| 2C slave device | Slave device | I2C address | I/O standard | Comment |

|---|---|---|---|---|

| IC14 | Temperature sensor | 1 0 0 1 0 0 0 RW | 3.3V | LM75 |

| IC15 | EEPROM | 1 0 1 0 0 0 0 RW | 3.3V | M24128 |

| IC19 | Clock generator | 1 1 0 0 0 0 0 RW | 3.3V | Si5351C |

| Schematic signal name | FPGA pin | I/O standard | Comment |

|---|---|---|---|

| FPGA_I2C_SDA | G16 | 3.3V | |

| FPGA_I2C_SCL | G17 | 3.3V |

- LMS_I2C: this interface has two EEPROMs. In Table 14 are listed all LMS_I2C slave devices and their information.

| I2C slave device | Slave device | I2C address | I/O standard | Comment |

|---|---|---|---|---|

| IC2 | EEPROM for LMS7 MCU firmware | 1 0 1 0 0 0 0 RW | 3.3V | M24128 |

| IC3 | EEPROM | 1 0 1 0 1 1 1 RW | 3.3V | 24FC512 |

LMS_I2C interface (LMS_I2C_SCL, LMS_I2C_SDA) is connected via 0R resistors to FPGA pins for debugging purposes, see Table 15.

| Schematic signal name | FPGA pin | I/O standard | Comment |

|---|---|---|---|

| LMS_I2C_SCL | G11 | 2.5V (3.3V) | 0R resistor R51 |

| LMS_I2C_SDA | A2 | 2.5V (3.3V) | 0R resistor R46 |

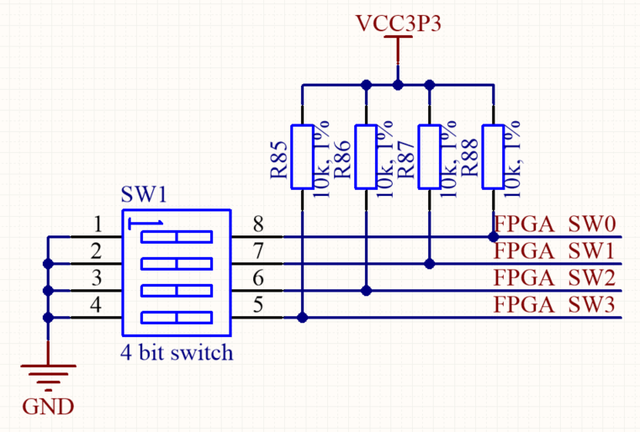

FPGA Switch

4 poles slide switch SW1 is connected to FPGA. Each switch line has external pull up resistors. When switch is in position “On”, it pulls down the line.

| Switch pole | Schematic signal name | FPGA pin | I/O standard |

|---|---|---|---|

| 1 | FPGA_SW0 | D22 | 3.3V |

| 2 | FPGA_SW1 | E21 | 3.3V |

| 3 | FPGA_SW2 | E22 | 3.3V |

| 4 | FPGA_SW3 | G22 | 3.3V |

RF loopback control

LimeSDR-PCIe v1.3 board contains RF loopback switches (IC4, IC5, IC6, IC7) for LMS7002M which are controlled from FPGA. By using loopback switches RF path TX1_2 can be connected to RX1_H and TX2_2 to RX2_H.

| Loopback path | Schematic signal name | FPGA pin | I/O standard |

|---|---|---|---|

| TX1_2 | TX1_2_LB_L | A22 | 3.3V |

| TX1_2_LB_H | A21 | 3.3V | |

| TX1_2_LB_SH | B20 | 3.3V | |

| TX2_2 | TX2_2_LB_L | B22 | 3.3V |

| TX2_2_LB_H | B21 | 3.3V | |

| TX2_2_LB_SH | C22 | 3.3V |

FPGA GPIO connectors

There are J12 and J13 connectors (pinheaders) there 8 + 8 FPGA GPIOs are connected (3.3V IO compatible) with GND and power pins (3.3V). In Table 18 are listed connector J12 pins and in Table 19 are listed connector J13 pins, corresponding FPGA pins and other information.

| Connector pin | Schematic signal name | FPGA pin | I/O standard | Comment |

|---|---|---|---|---|

| 1 | FPGA_GPIO0 | B12 | 3.3V | |

| 2 | FPGA_GPIO1 | C16 | 3.3V | |

| 3 | FPGA_GPIO2 | B15 | 3.3V | |

| 4 | FPGA_GPIO3 | B13 | 3.3V | |

| 5 | FPGA_GPIO4 | A15 | 3.3V | |

| 6 | FPGA_GPIO5 | B16 | 3.3V | |

| 7 | FPGA_GPIO6 | A17 | 3.3V | |

| 8 | FPGA_GPIO7 | A16 | 3.3V | |

| 9 | GND | - | Ground | |

| 10 | VCC3P3 | - | Power net (3.3V) |

| Connector pin | Schematic signal name | FPGA pin | I/O standard | Comment |

|---|---|---|---|---|

| 1 | FPGA_GPIO8 | G15 | 3.3V | |

| 2 | FPGA_GPIO9 | G14 | 3.3V | |

| 3 | FPGA_GPIO10 | D14 | 3.3V | |

| 4 | FPGA_GPIO11 | D15 | 3.3V | |

| 5 | FPGA_GPIO12 | C14 | 3.3V | |

| 6 | FPGA_GPIO13 | C15 | 3.3V | |

| 7 | FPGA_GPIO14 | C12 | 3.3V | |

| 8 | FPGA_GPIO15 | C13 | 3.3V | |

| 9 | GND | - | Ground | |

| 10 | VCC3P3 | - | Power net (3.3V) |

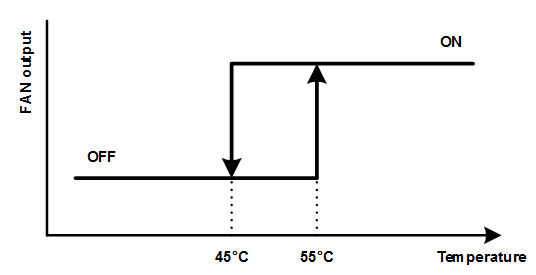

Board temperature control

LimeSDR-PCIe has integrated temperature sensor which can control FAN to keep board in operating temperature range. FAN must be connected to J14 (0.1” pitch) connector. FAN control voltage is 12V. Fan will be turned on if board will heat up to 55°C and FAN will be turned off if board will cool down to 45°C. FAN control temperature range is set by FPGA.

Temperature sensor output (LM75_OS) is connected to FPGA pin K14. FAN MOSFET can be controlled from FPGA pin K13 (FAN_CTRL). More detailed information about FAN control is presented in Figure 4.

Measured temperature value can be read by using LMS7suite.

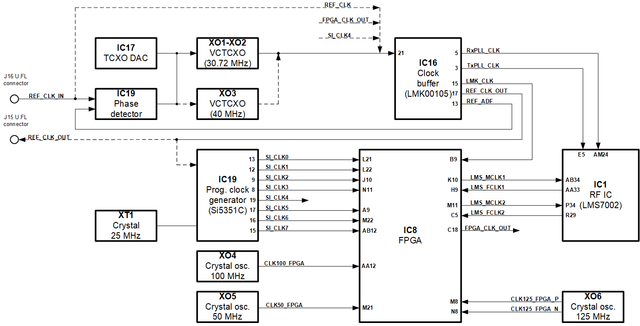

Clock Distribution

LimeSDR-PCIe board clock distribution block diagram is presented in Figure 8.

LimeSDR-PCIe board has onboard 30.72 MHz ±250 ppb VCTCXO that is reference clock for LMS_PLLs. See block diagram of the clock distribution system in Figure 8.

VCTCXO can be tuned by onboard phase detector (IC18, ADF4002 [link]) or by DAC (IC17). The onboard phase detector is used to synchronize onboard VCTCXO with external equipment (via J16 U.FL connector) to calibrate frequency error. At the same time only ADF or DAC can control VCTCXO. DAC and ADF is controlled by FPGA and selection between ADF and DAC is done automatically. When board is powered, by default VCTCXO is controlled by DAC.

J16 connector (REF_CLK_IN) can also be used to supply external reference clock (fitting R109, removing R107, C347).

J15 connector (REF_CLK_OUT) can be used to feed clock to another board for synchronization purposes. For this purpose R122 resistor has to be fitted.

External reference clock frequency range is 5 MHz - 400 MHz. For frequencies less than 5 MHz, ensure slew rate is more than 4 V/μ. This is a CMOS input with a nominal threshold of VDD/2 (3.3 V / 2 = 1.65 V) and a DC equivalent input resistance of 100 kΩ. This input can be driven from a TTL or CMOS crystal oscillator or it can be AC-coupled.

The programmable clock generator (IC19, Si5351C [link]) can generate any reference clock frequency, starting from 8 kHz – 160 MHz, for FPGA and LMS PLLs.

How to configure clocks using LMS7Suite read in chapter 7.4 Clock configuration.

| Source | Schematic signal name | I/O standard | FPGA pin | Description |

|---|---|---|---|---|

| Programmable clock generator (IC19) | SI_CLK0 | 2.5V (3.3V) | M7 | |

| SI_CLK1 | 2.5V (3.3V) | N7 | ||

| SI_CLK2 | 2.5V (3.3V) | N8 | ||

| SI_CLK3 | 2.5V (3.3V) | J10 | ||

| SI_CLK4 | 3.3V | - | Can be used as reference clock | |

| SI_CLK6 | 3.3V | L22 | ||

| Clock buffer (IC16) | LMK_CLK | 3.3V | B9 | Reference clock (30.72 MHz) |

| RF transceiver (IC1) | LMS_MCLK1 | 2.5V (3.3V) | K10 | |

| LMS_FCLK1 | 2.5V (3.3V) | H9 | ||

| LMS_MCLK2 | 2.5V (3.3V) | M8 | ||

| LMS_FCLK2 | 2.5V (3.3V) | C5 | ||

| FPGA (IC8) | FPGA_CLK_OUT | 3.3V | C18 | Can be used as reference clock |

Power Distribution

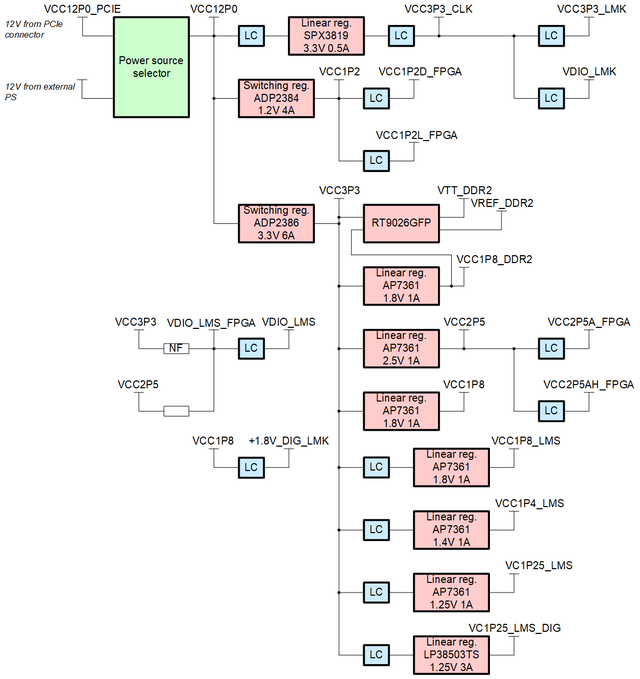

LimeSDR-PCIe board power distribution block diagram is presented in Figure 9.

LimeSDR-PCIe board is powered from PCIe port (12V). Switching and linear regulators are used to make other required voltages.

| |||||||||||||||||||||