Lime-GPSDO: Difference between revisions

Jump to navigation

Jump to search

| Line 49: | Line 49: | ||

* [https://github.com/myriadrf/ PCB project (Altium project) TBD ] | * [https://github.com/myriadrf/ PCB project (Altium project) TBD ] | ||

* [https://github.com/myriadrf/ BOM (XLS) TBD] | * [https://github.com/myriadrf/ BOM (XLS) TBD] | ||

== Additional Components == | |||

Here is a list of additional components to be used with LimeSDR-Mini board. | |||

* TBD | |||

{{Community}} | |||

Revision as of 12:42, 10 April 2019

Lime-GPSDO Boards

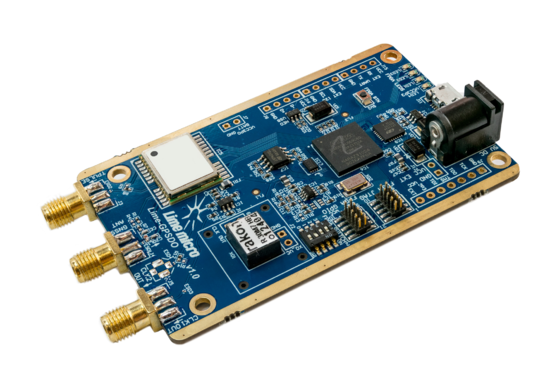

Lime-GPSDO is a combination of GPS receiver, high-quality clock source (VCOCXO) and Intel MAX10 FPGA fitted in one board which can be used as high stability clock source for timing sensitive applications.

Lime-GPSDO v1.0 board

Features and Specifications

| Feature | Description |

|---|---|

| FPGA | Intel MAX 10 (10M16SAU169C8G 169-UBGA) |

| USB-to-UART bridge | Silicon labs USBXpress Family CP2102N |

| Oscillator | Rakon U7475LF @30.72MHz |

| GPS receiver | TBD |

| RF connection | 3 SMA connectors (Time pulse, GNSS antena, Clock output) |

| Status indicators | x3 Programmable LEDs |

| Dimensions | 50.50mm x 80mm |

Getting Help

If you have questions, the MyriadRF Discourse is a best place to ask for help.

Documentation

FPGA Binaries

Here are the links to pre-compiled FPGA gateware (bitstream):

- FPGA TBD

Board Design Files

Here are links to the schematic, PCB project and BOM:

Lime-GPSDO v1.0

Additional Components

Here is a list of additional components to be used with LimeSDR-Mini board.

- TBD

| |||||||||||||||||||||