Novena-RF: Difference between revisions

Ghalfacree (talk | contribs) (Created pin-out table from diagram.) |

AndrewBack (talk | contribs) No edit summary |

||

| (One intermediate revision by the same user not shown) | |||

| Line 12: | Line 12: | ||

{| class="wikitable" | {| class="wikitable" | ||

|Transceiver | |Transceiver | ||

|LMS6002D | |[[LimeMicro:LMS6002D_Datasheet|LMS6002D]] | ||

|- | |- | ||

|RF Bandwidth (BW) | |RF Bandwidth (BW) | ||

| Line 148: | Line 148: | ||

* [[Reference Development Kit]] | * [[Reference Development Kit]] | ||

* [https://myriadrf.org/projects/novena-rf/ Novena-RF Project Page] | * [https://myriadrf.org/projects/novena-rf/ Novena-RF Project Page] | ||

{{Community}} | |||

Latest revision as of 20:23, 15 September 2015

About

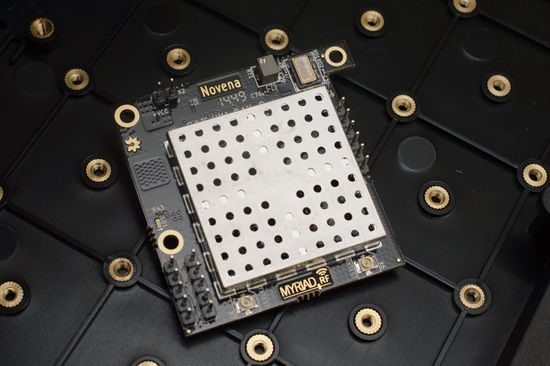

The Novena-RF module is based on the original Myriad-RF 1 design and has been adapted for use with the Novena open hardware computing platform, which can be configured for embedded applications and as an all-in-one desktop or a laptop.

Images

-

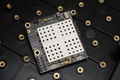

Novena-RF board

-

Novena-RF board, installed

Specifications

| Transceiver | LMS6002D |

| RF Bandwidth (BW) | 300 MHz to 3800 MHz |

| Baseband Bandwidth (BW) | Programmable (16 selections:; 0.75 – 14 MHz, Bypass mode |

| RF Module Control | Via Serial Peripheral Interface (SPI) |

| Clock | TCXO and option for Novena to supply the interface clock |

| RF Connectors | U.FL micro-coax to bulkhead SMA on Novena port farm |

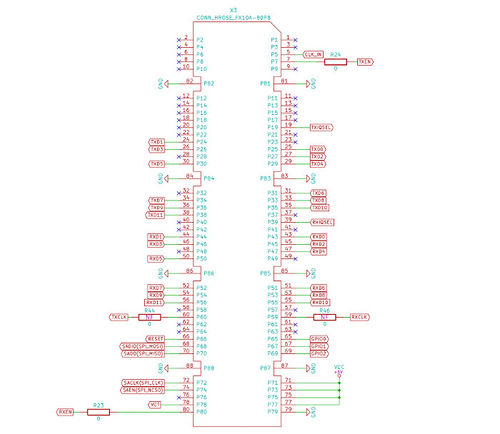

Connections

| Pin Nr | Function | Description | Pin Nr | Function | Description |

|---|---|---|---|---|---|

| 1 | NC | No connection | 2 | NC | No connection |

| 3 | NC | No connection | 4 | NC | No connection |

| 5 | CLK_IN | Clock input | 6 | NC | No connection |

| 7 | TXEN | CMOS In | 8 | NC | No connection |

| 9 | NC | No connection | 10 | NC | No connection |

| 81 | GND | Power | 82 | GND | Power |

| 11 | NC | No connection | 12 | NC | No connection |

| 13 | NC | No connection | 14 | NC | No connection |

| 15 | NC | No connection | 16 | NC | No connection |

| 17 | NC | No connection | 18 | NC | No connection |

| 19 | TXIQSEL | CMOS Out | 20 | NC | No connection |

| 21 | NC | No connection | 22 | NC | No connection |

| 23 | NC | No connection | 24 | TXD1 | CMOS IO |

| 25 | TXD0 | CMOS IO | 26 | TXD3 | CMOS IO |

| 27 | TXD2 | CMOS IO | 28 | NC | No connection |

| 29 | TXD4 | CMOS IO | 30 | TXD5 | CMOS IO |

| 83 | GND | Power | 84 | GND | Power |

| 31 | TXD6 | CMOS IO | 32 | NC | No connection |

| 33 | TXD8 | CMOS IO | 34 | TXD7 | CMOS IO |

| 35 | TXD10 | CMOS IO | 36 | TXD9 | CMOS IO |

| 37 | NC | No connection | 38 | TXD11 | CMOS IO |

| 39 | RXIQSEL | CMOS In | 40 | NC | No connection |

| 41 | NC | No connection | 42 | NC | No connection |

| 43 | RXD0 | CMOS IO | 44 | RXD1 | CMOS IO |

| 45 | RXD2 | CMOS IO | 46 | RXD3 | CMOS IO |

| 47 | RXD4 | CMOS IO | 48 | NC | No connection |

| 49 | NC | No connection | 50 | RXD5 | CMOS IO |

| 85 | GND | Power | 86 | GND | Power |

| 51 | RXD6 | CMOS IO | 52 | RXD7 | CMOS IO |

| 53 | RXD8 | CMOS IO | 54 | RXD9 | CMOS IO |

| 55 | RXD10 | CMOS IO | 56 | RXD11 | CMOS IO |

| 57 | NC | No connection | 58 | NC | No connection |

| 59 | RXCLK | Receive Clock | 60 | TXCLK | Transmit Clock |

| 61 | NC | No connection | 62 | NC | No connection |

| 63 | NC | No connection | 64 | NC | No connection |

| 65 | GPIO0 | CMOS In | 66 | RESET | CMOS In |

| 67 | GPIO1 | CMOS In | 68 | SPI_MOSI | CMOS In |

| 69 | GPIO2 | CMOS In | 70 | SPI_MISO | CMOS Out |

| 87 | GND | Power | 88 | GND | Power |

| 71 | +5V | Power | 72 | SPI_CLK | CMOS In |

| 73 | +5V | Power | 74 | SPI_NCS0 | CMOS In |

| 75 | +5V | Power | 76 | NC | No connection |

| 77 | +5V | Power | 78 | VC1 | - |

| 79 | GND | Power | 80 | RXEN | CMOS In |

Schematics

-

RF circuits

-

Analogue circuits

-

Clocks, RF FE

-

Connectors

-

Digital circuits

-

Power supply

Driver

A complete software defined radio (SDR) driver for the Novena-RF module is available via GitHub. For more information on the use of this driver, see the Novena-RF Driver page.

Licensing

Hardware

The hardware designs are licensed under a Creative Commons Attribution 3.0 Unported licence.

Gateware

The FPGA RTL is licensed under the Apache License, Version 2.0. However, please note that this does not extend to any files provided with the Xilinx design tools; see the relevant files for the associated terms and conditions.

See Also

| |||||||||||||||||||||