Zipper Interface Board: Difference between revisions

Ghalfacree (talk | contribs) (Added schematics as a gallery.) |

AndrewBack (talk | contribs) No edit summary |

||

| (3 intermediate revisions by one other user not shown) | |||

| Line 1: | Line 1: | ||

===About=== | ===About=== | ||

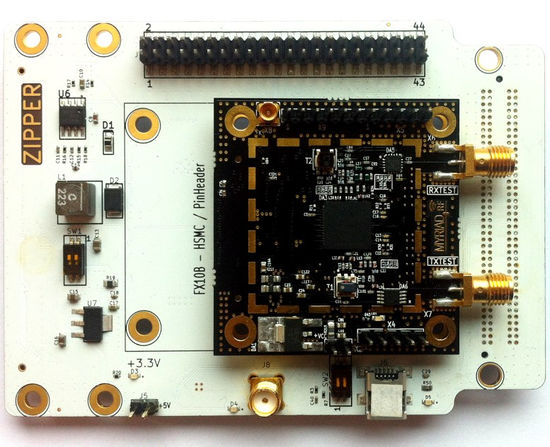

The Zipper Interface Board is designed to allow any Field-Programmable Gate Array (FPGA) development system supporting the High-Speed Mezzanine Card (HSMC) or FPGA Mezzanine Card (FMC) standards to be connected to the [[Myriad- | [[File:Zipper-1.jpg|center|550px|Zipper Interface Board, top]] | ||

The Zipper Interface Board is designed to allow any Field-Programmable Gate Array (FPGA) development system supporting the High-Speed Mezzanine Card (HSMC) or FPGA Mezzanine Card (FMC) standards to be connected to the [[Myriad-RF 1]] to form the [[Reference Development Kit]]. The combination of the Zipper and Myriad-RF 1 boards provides a low-cost universal radio development platform, based on the flexible, multi-standard Field Programmable Radio Frequency (FPRF) LMS6002D device. It enables developers to implement their products for a wide variety of wireless communication applications efficiently. | |||

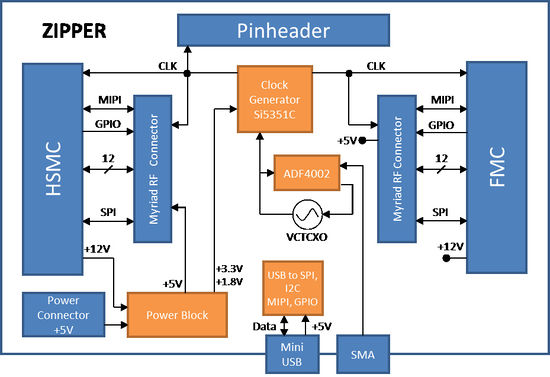

===Block diagram=== | |||

[[File:Zipper-Block-Diagram.jpg|center|550px|Zipper Interface Board block diagram]] | |||

===Connections=== | ===Connections=== | ||

| Line 22: | Line 21: | ||

File:Zipper-Interface-Board-Schematics-8.png|ADF4002 | File:Zipper-Interface-Board-Schematics-8.png|ADF4002 | ||

</gallery> | </gallery> | ||

===Licensing=== | |||

====Hardware==== | |||

The hardware designs are licensed under a [https://creativecommons.org/licenses/by/3.0/ Creative Commons Attribution 3.0 Unported] licence. | |||

====Firmware==== | |||

The firmware is licensed under the [https://www.gnu.org/licenses/gpl-3.0.en.html GNU General Public Licence, Version 3]. Please note that third-party dependencies and modules may have their own licensing requirements. | |||

===See Also=== | ===See Also=== | ||

| Line 27: | Line 33: | ||

* [[Zipper Interface Board Connections]] | * [[Zipper Interface Board Connections]] | ||

* [https://myriadrf.org/projects/rdk/ Reference Development Kit Project Page] | * [https://myriadrf.org/projects/rdk/ Reference Development Kit Project Page] | ||

{{Community}} | |||

Latest revision as of 15:05, 15 September 2015

About

The Zipper Interface Board is designed to allow any Field-Programmable Gate Array (FPGA) development system supporting the High-Speed Mezzanine Card (HSMC) or FPGA Mezzanine Card (FMC) standards to be connected to the Myriad-RF 1 to form the Reference Development Kit. The combination of the Zipper and Myriad-RF 1 boards provides a low-cost universal radio development platform, based on the flexible, multi-standard Field Programmable Radio Frequency (FPRF) LMS6002D device. It enables developers to implement their products for a wide variety of wireless communication applications efficiently.

Block diagram

Connections

The Zipper Interface Board features numerous on-board connections, in addition to those available on the Myriad-RF 1 itself. A full list of available connections is available on the page Zipper Interface Board Connections.

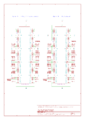

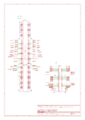

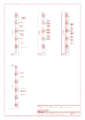

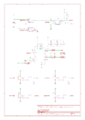

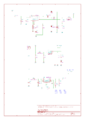

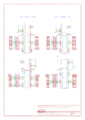

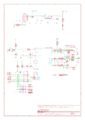

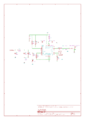

Schematics

-

Data interface connector

-

HSMC & pin header connectors

-

FMC connector

-

Clock generator

-

Power supply

-

Buffers

-

Microcontroller

-

ADF4002

Licensing

Hardware

The hardware designs are licensed under a Creative Commons Attribution 3.0 Unported licence.

Firmware

The firmware is licensed under the GNU General Public Licence, Version 3. Please note that third-party dependencies and modules may have their own licensing requirements.

See Also

| |||||||||||||||||||||