Uncategorized files

Jump to navigation

Jump to search

Showing below up to 100 results in range #51 to #150.

-

Clocktamer lvds at usrp.png 800 × 539; 37 KB

-

Close WX GUI Button GnuRadio.png 743 × 504; 61 KB

-

DC offset block control.png 1,185 × 708; 242 KB

-

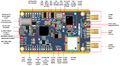

DE0-Nano-1.jpg 470 × 345; 74 KB

-

DE0-Nano-Connections.jpg 622 × 530; 54 KB

-

DE0-Nano-Interface-Board-1.jpg 587 × 530; 157 KB

-

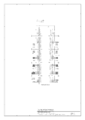

DE0-Nano-Interface-Board-Schematics-1.png 2,480 × 3,508; 144 KB

-

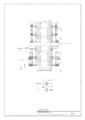

DE0-Nano-Interface-Board-Schematics-2.png 2,480 × 3,508; 222 KB

-

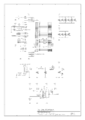

DE0-Nano-Interface-Board-Schematics-3.png 2,480 × 3,508; 194 KB

-

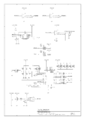

DE0-Nano-Interface-Board-Schematics-4.png 2,480 × 3,508; 171 KB

-

DE0-Nano-Interface-Board-Schematics-5.png 2,480 × 3,508; 65 KB

-

DE0-Nano-Interface-Board-Schematics-6.png 2,480 × 3,508; 88 KB

-

DE0-Nano-J2.jpg 444 × 886; 61 KB

-

DE0-Nano-J4.jpg 439 × 343; 15 KB

-

DE0-Nano-J6.jpg 640 × 394; 18 KB

-

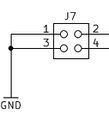

DE0-Nano-J7.jpg 254 × 280; 6 KB

-

DE0-Nano-J8-J9.jpg 454 × 534; 12 KB

-

DE0-Nano-JA1.jpg 927 × 873; 127 KB

-

DE0interfaceboard-Assembled-1.jpg 337 × 302; 57 KB

-

DVB-T transmitter example.png 1,263 × 516; 121 KB

-

Digired-clock-generator.png 616 × 899; 56 KB

-

Digired-connectors.png 616 × 899; 62 KB

-

Digired-digital-interface.png 616 × 899; 38 KB

-

Digired-power-supply.png 616 × 899; 51 KB

-

Digired-usb3-interface.png 617 × 899; 50 KB

-

Documentation Tab GnuRadio.png 500 × 528; 44 KB

-

Enable DC corrector in RxTSP.png 1,185 × 709; 259 KB

-

Enable the test NCO.png 1,187 × 706; 243 KB

-

Example.png 384 × 190; 25 KB

-

FFTviewer Controls.png 679 × 476; 80 KB

-

FFTviewer window in operation.png 712 × 791; 130 KB

-

FM Receiver Example GnuRadio.png 1,183 × 491; 93 KB

-

FM Transmitter Example GnuRadio.png 888 × 495; 70 KB

-

FREEBSD Logo Horiz Pos RGB.png 570 × 164; 33 KB

-

FX3 after custom firmware is downloaded.png 701 × 610; 161 KB

-

FX3 programing options.png 893 × 261; 61 KB

-

Figure 10 Lime-GPSDO board power distribution block diagram.png 677 × 183; 10 KB

-

Figure 11 LimeSDR-QPCIe v1.2 Dedicated FAN mounting space.png 433 × 432; 226 KB

-

Figure 12 LimeSDR-QPCIe v1.2 board clock distribution block diagram.png 1,457 × 1,186; 85 KB

-

Figure 13 LimeSDR-QPCIe v1.2 board power distribution block diagrams.png 3,473 × 1,643; 536 KB

-

Figure 14 LimeSDR-QPCIe v1.2 board power ICs on TOP side.png 763 × 471; 475 KB

-

Figure 15 LimeSDR-QPCIe v1.2 board power ICs on BOTTOM side.png 767 × 473; 505 KB

-

Figure 1 Lime-GPSDO top side components and connectors.png 2,247 × 1,237; 815 KB

-

Figure 2 Bottom side components.png 1,243 × 832; 351 KB

-

Figure 3 Lime-GPSDO Development Board Block Diagram.png 869 × 373; 20 KB

-

Figure 4 Time pulse output selection.png 1,455 × 904; 95 KB

-

Figure 5 Power rail selection for pin 10 of J12 connector.png 1,252 × 911; 96 KB

-

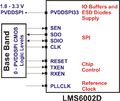

Figure 6 Communication interfaces.png 868 × 362; 15 KB

-

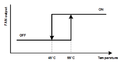

Figure 7 FAN control temperature hysteresis.png 536 × 275; 5 KB

-

Figure 8 Lime-GPSDO board clock distribution block diagram.png 793 × 410; 16 KB

-

Figure 9 LimeSDR-QPCIe v1.2 indication LEDs.png 463 × 382; 120 KB

-

Figure 9 SMA connector J6 source selection.png 1,336 × 759; 70 KB

-

Freebsd-128-128.png 132 × 128; 36 KB

-

Freebsd-logo.png 178 × 175; 32 KB

-

GFSK loopback example.png 990 × 481; 105 KB

-

Git logo.png 155 × 80; 4 KB

-

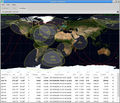

Gpredict 1 768w.jpg 768 × 656; 164 KB

-

Grc xmit only.jpg 781 × 246; 39 KB

-

IQ Corrector block control.png 1,186 × 708; 243 KB

-

KiCAD footprints.png 700 × 478; 321 KB

-

Kill Flow Graph Button GnuRadio.png 141 × 36; 4 KB

-

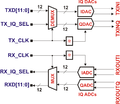

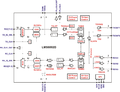

LMS6002D-Baseband-Data-Interface.png 1,324 × 1,149; 121 KB

-

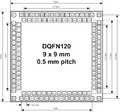

LMS6002D-DQFN120-Package-Top-View.png 1,386 × 1,298; 153 KB

-

LMS6002D-Digital-IQ-Interface-Supplies.png 1,146 × 1,196; 155 KB

-

LMS6002D-Frame-Sync-Polarity-Interleave-Modes.png 2,262 × 1,210; 166 KB

-

LMS6002D-Functional-Block-Diagram.png 3,149 × 2,425; 475 KB

-

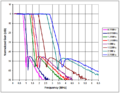

LMS6002D-LPF-Amplitude-Response-1.png 706 × 546; 34 KB

-

LMS6002D-LPF-Amplitude-Response-2.png 706 × 546; 34 KB

-

LMS6002D-PLL-Architecture.png 1,927 × 1,446; 106 KB

-

LMS6002D-PLL-Reference-Clock-Input-Buffer-AC-Coupled.png 1,820 × 1,734; 95 KB

-

LMS6002D-PLL-Reference-Clock-Input-Buffer-DC-Coupled.png 1,820 × 1,734; 95 KB

-

LMS6002D-RX-Data-Interface-Signals.png 2,338 × 1,637; 151 KB

-

LMS6002D-RX-Data-Interface.png 1,909 × 1,533; 192 KB

-

LMS6002D-RX-Gain-Control-Architecture.png 1,581 × 602; 109 KB

-

LMS6002D-SPI-Read-Cycle-3-Wire.png 4,916 × 909; 200 KB

-

LMS6002D-SPI-Read-Cycle-4-Wire.png 4,927 × 1,271; 230 KB

-

LMS6002D-SPI-Supplies.png 1,157 × 972; 115 KB

-

LMS6002D-SPI-Write-Cycle.png 4,916 × 881; 189 KB

-

LMS6002D-TX-Data-Interface.png 1,743 × 1,481; 190 KB

-

LMS6002D-TX-Gain-Control-Architecture.png 1,575 × 550; 91 KB

-

LMS6002D-TX-IQ-Interface-Signals.png 2,327 × 1,700; 150 KB

-

LMS6002D-Typical-Application-Circuit-RF-Part.png 683 × 730; 41 KB

-

LMS6002D FAQ Ramp Rate.png 639 × 397; 37 KB

-

LMS6002D FAQ VCO Frequency Range.png 1,399 × 743; 29 KB

-

LMS6002Dr2-DC-Offset-Calibration-LPF-Tuning-Module.png 427 × 650; 19 KB

-

LMS6002Dr2-Envelop-Pick-Detector.png 1,868 × 2,699; 146 KB

-

LMS6002Dr2-General-DC-Calibration.png 382 × 780; 20 KB

-

LMS6002Dr2-IQ-Gain-Correction.png 223 × 184; 5 KB

-

LMS6002Dr2-IQ-Phase-Correction.png 340 × 252; 7 KB

-

LMS6002Dr2-LPF-Bandwidth-Tuning.png 521 × 620; 26 KB

-

LMS6002Dr2-Loopback-Test.png 3,000 × 1,898; 539 KB

-

LMS6002Dr2-PLL-Control.png 2,572 × 1,705; 201 KB

-

LMS6002Dr2-RX-I-Q-DC-Level-Correction.png 265 × 207; 6 KB

-

LMS6002Dr2-RXFE-Control.png 3,000 × 2,619; 590 KB

-

LMS6002Dr2-RXVGA2-Control.png 2,517 × 1,696; 292 KB

-

LMS6002Dr2-RXVGA2-DC-Offset-Calibration.png 793 × 627; 45 KB

-

LMS6002Dr2-TXRF-Control.png 3,465 × 2,678; 444 KB

-

LMS6002Dr2-TXRX-LPF-Control.png 1,390 × 1,110; 158 KB

-

LMS6002Dr2-TXRX-LPF-DC-Offset-Calibration.png 424 × 760; 25 KB

-

LMS6002Dr2-VCO-Capacitance-Selection.png 2,287 × 1,659; 178 KB