Uploads by Ghalfacree

Jump to navigation

Jump to search

This special page shows all uploaded files.

| Date | Name | Thumbnail | Size | Description | Versions |

|---|---|---|---|---|---|

| 10:01, 1 October 2015 | LMS6002D-LPF-Amplitude-Response-1.png (file) |  |

34 KB | Higher-resolution version. | 2 |

| 10:01, 1 October 2015 | LMS6002D-LPF-Amplitude-Response-2.png (file) |  |

34 KB | Higher-resolution version. | 2 |

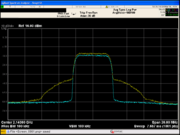

| 22:46, 3 June 2017 | Adpd-test-case-1-pa-output-spectrum.png (file) |  |

35 KB | ADPD test case 1, PA output spectrum. | 1 |

| 17:22, 2 June 2016 | Lms7002m-limelight-trxiq-sdr-receive-data-path.png (file) | 35 KB | LMS7002M LimeLight TRXIQ SDR mode receive data path timing diagram. | 1 | |

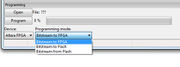

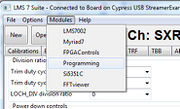

| 19:37, 4 May 2016 | LimeSDR-USB-LMS-7-Suite-Modules-Programming-Mode.jpg (file) |  |

35 KB | Choosing a programming mode in the LMS 7 Suite. | 1 |

| 15:55, 1 June 2016 | Lms7002m-rx-gain-control-architecture.png (file) |  |

35 KB | LMS7002M RX gain control architecture diagram. | 1 |

| 20:34, 3 May 2016 | LimeSDR-USB-Windows-USB-Driver-Installation-2.jpg (file) |  |

36 KB | LimeSDR-USB Windows driver installation, step two. | 1 |

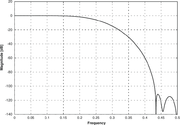

| 16:12, 2 June 2016 | Lms7002m-tsp-hb2-amplitude-response.png (file) |  |

36 KB | LMS7002M HB2 amplitude response graph. | 1 |

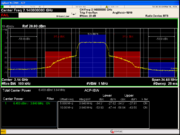

| 22:50, 3 June 2017 | Adpd-test-case-1-acpr-with-adpd.png (file) |  |

37 KB | ADPD test case 1, ACPR with ADPD. | 1 |

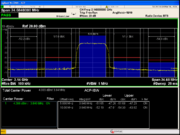

| 22:48, 3 June 2017 | Adpd-test-case-1-acpr-without-adpd.png (file) |  |

37 KB | ADPD test case 1, ACPR without ADPD. | 1 |

| 20:06, 2 June 2016 | Lms7002m-spi-write-cycle-timing.png (file) | 38 KB | LMS7002M SPI write cycle timing diagram | 1 | |

| 17:22, 2 June 2016 | Lms7002m-limelight-trxiq-ddr-transmit-data-path.png (file) | 38 KB | LMS7002M LimeLight TRXIQ DDR mode transmit data path timing diagram. | 1 | |

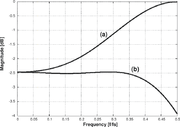

| 15:25, 2 June 2016 | Lms7002m-tsp-invsinc-dac-amplitude.png (file) |  |

39 KB | LMS7002M INVSINC (a) and corresponding DAC (b) amplitude response graph. | 1 |

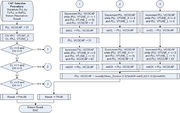

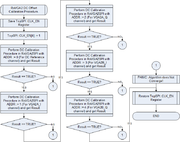

| 15:44, 13 October 2015 | LMS6002Dr2-VCO-VCOCAP-Code-Selection-Algorithm-VCOCAP-Selection.png (file) |  |

39 KB | Improved graphic. | 2 |

| 17:21, 2 June 2016 | Lms7002m-limelight-trxiq-ddr-receive-data-path.png (file) | 40 KB | LMS7002M LimeLight TRXIQ DDR mode receive data path timing diagram. | 1 | |

| 10:05, 1 October 2015 | LMS6002D-Typical-Application-Circuit-RF-Part.png (file) |  |

41 KB | Higher-resolution version. | 2 |

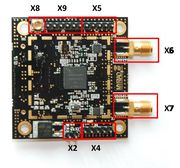

| 15:51, 16 July 2015 | MyriadRF1-Connectors-Top.jpg (file) |  |

42 KB | Myriad-RF 1 Board, with connectors labelled - top side. | 1 |

| 20:30, 2 June 2016 | Lms7002m-clock-generation.png (file) |  |

43 KB | LMS7002M clock generation diagram | 1 |

| 20:07, 2 June 2016 | Lms7002m-spi-read-cycle-3-wire-timing.png (file) | 44 KB | LMS7002M SPI read cycle, 3-wire timing diagram | 1 | |

| 14:52, 6 October 2015 | LMS6002Dr2-RXVGA2-DC-Offset-Calibration.png (file) |  |

45 KB | Clearer image. | 2 |

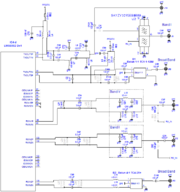

| 20:05, 3 May 2016 | LimeSDR-USB-Clock-Distribution.jpg (file) |  |

46 KB | Block diagram for the LimeSDR-USB v1.2's clock distribution. | 1 |

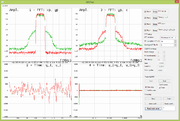

| 22:44, 3 June 2017 | Adpd-test-case-1-signals-after-training.png (file) |  |

47 KB | ADPD test case 1, signals after training. | 1 |

| 15:51, 16 July 2015 | MyriadRF1-Connectors-Bottom.jpg (file) |  |

47 KB | Myriad-RF 1 Board with connectors labelled - bottom side. | 1 |

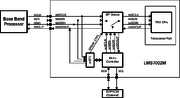

| 20:23, 2 June 2016 | Lms7002m-mcu-connections.png (file) |  |

49 KB | LMS7002M on-chip microcontroller connection diagram | 1 |

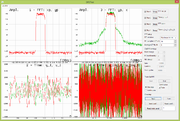

| 22:42, 3 June 2017 | Adpd-test-case-1-signals-before-training.png (file) |  |

50 KB | ADPD test case 1, signals before training. | 1 |

| 17:20, 2 June 2016 | Lms7002m-limelight-jesd207-receive-burst-finish.png (file) | 50 KB | LMS7002M LimeLight JESD207 mode receive burst finish timing diagram. | 1 | |

| 17:18, 2 June 2016 | Lms7002m-limelight-jesd207-transmit-burst-finish.png (file) | 50 KB | LMS7002M LimeLight JESD207 mode transmit burst finish timing diagram. | 1 | |

| 20:51, 3 May 2016 | LimeSDR-USB-Windows-USB-Driver-Installation-4.jpg (file) |  |

51 KB | LimeSDR-USB Windows driver installation, step 4. | 1 |

| 20:07, 2 June 2016 | Lms7002m-spi-read-cycle-4-wire-timing.png (file) | 51 KB | LMS7002M SPI read cycle, 4-wire (default) timing | 1 | |

| 22:52, 3 June 2017 | Adpd-test-case-1-evm-with-adpd.png (file) |  |

52 KB | ADPD test case 1, EVM with ADPD. | 1 |

| 16:10, 2 June 2016 | Lms7002m-tsp-hb1-impulse-response.png (file) |  |

52 KB | LMS7002M HB1 impulse response figures. | 1 |

| 20:27, 3 May 2016 | LimeSDR-USB-Windows-USB-Driver-Installation-1-Continued.jpg (file) |  |

53 KB | LimeSDR-USB Windows driver installation, step one (continued.) | 1 |

| 22:51, 3 June 2017 | Adpd-test-case-1-evm-without-adpd.png (file) |  |

53 KB | ADPD test case 1, EVM without ADPD. | 1 |

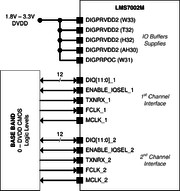

| 17:27, 2 June 2016 | Lms7002m-digital-iq-interface-supplies.png (file) |  |

54 KB | LMS7002M digital IQ interface supplies diagram. | 1 |

| 16:04, 16 July 2015 | DE0-Nano-Connections.jpg (file) |  |

54 KB | DE0-Nano Interface Board with connections labelled. | 1 |

| 14:56, 2 June 2016 | Lms7002m-tsp-tx.png (file) | 54 KB | LMS7002M TXTSP structure diagram. | 1 | |

| 19:59, 3 May 2016 | LimeSDR-USB-FPGA-Low-Speed-Interfaces-Block-Diagram.jpg (file) |  |

55 KB | Block diagram for the FPGA low-speed interfaces on the LimeSDR-USB v1.2. | 1 |

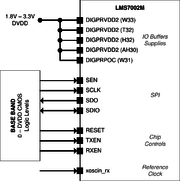

| 20:21, 2 June 2016 | Lms7002m-spi-supplies.png (file) |  |

55 KB | LMS7002M SPI supplies diagram | 1 |

| 14:59, 29 April 2018 | Limesdr-mini-test-linux-gui.png (file) |  |

55 KB | LimeQuickTest running in GUI mode on Ubuntu 16.04.3. | 1 |

| 17:17, 2 June 2016 | Lms7002m-limelight-jesd207-transmit-burst-start.png (file) | 55 KB | LMS7002M LimeLight JESD207 mode transmit burst start timing diagram. | 1 | |

| 17:19, 2 June 2016 | Lms7002m-limelight-jesd207-receive-burst-start.png (file) | 55 KB | LMS7002M LimeLight JESD207 mode receive burst start timing diagram. | 1 | |

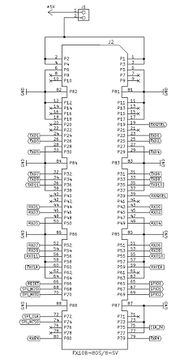

| 15:08, 22 July 2015 | Parallella-RF.png (file) |  |

55 KB | Parallella-RF circuit design. | 1 |

| 13:34, 16 July 2015 | RFDIO-Figure2.jpg (file) |  |

56 KB | Figure 2 from the RFDIO Connector Specification, Revision 1.0.1. | 1 |

| 19:36, 4 May 2016 | LimeSDR-USB-LMS-7-Suite-Modules-Programming.jpg (file) |  |

57 KB | LMS 7 Suite software showing the Modules menu. | 1 |

| 16:50, 13 July 2015 | DE0interfaceboard-Assembled-1.jpg (file) |  |

57 KB | DE0-Nano Interface Board, assembled with DE0-Nano and Myriad-RF1. | 1 |

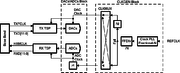

| 15:30, 3 June 2017 | Adpd-indirect-learning-architecture-block-diagram.png (file) |  |

60 KB | ADPD indirect learning architecture, block diagram. | 1 |

| 16:35, 16 July 2015 | DE0-Nano-J2.jpg (file) |  |

61 KB | DE0-Nano J2 connector pin-out. | 1 |

| 14:55, 2 June 2016 | Lms7002m-tsp-rx.png (file) | 61 KB | LMS7002M RXTSP structure diagram. | 1 | |

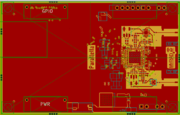

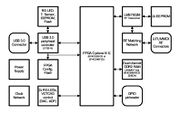

| 16:40, 3 May 2016 | LimeSDR-USB-Block-Diagram.jpg (file) |  |

62 KB | LimeSDR-USB block diagram. | 1 |

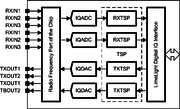

| 14:48, 2 June 2016 | Lms7002m-tsp.png (file) |  |

64 KB | LMS7002M Transceiver Signal Processor (TSP) block diagram. | 1 |