File list

Jump to navigation

Jump to search

This special page shows all uploaded files.

| Date | Name | Thumbnail | Size | User | Description | Versions |

|---|---|---|---|---|---|---|

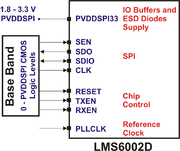

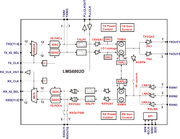

| 10:05, 1 October 2015 | LMS6002D-SPI-Supplies.png (file) |  |

115 KB | Ghalfacree | Higher-resolution version. | 2 |

| 10:04, 1 October 2015 | LMS6002D-Digital-IQ-Interface-Supplies.png (file) |  |

155 KB | Ghalfacree | Higher-resolution version. | 2 |

| 10:04, 1 October 2015 | LMS6002D-RX-Data-Interface-Signals.png (file) |  |

151 KB | Ghalfacree | Higher-resolution version. | 2 |

| 10:03, 1 October 2015 | LMS6002D-RX-Data-Interface.png (file) |  |

192 KB | Ghalfacree | Higher-resolution version. | 2 |

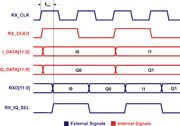

| 10:03, 1 October 2015 | LMS6002D-TX-IQ-Interface-Signals.png (file) |  |

150 KB | Ghalfacree | Higher-resolution version. | 2 |

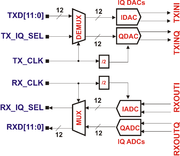

| 10:03, 1 October 2015 | LMS6002D-TX-Data-Interface.png (file) |  |

190 KB | Ghalfacree | Higher-resolution version. | 2 |

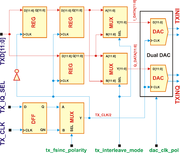

| 10:02, 1 October 2015 | LMS6002D-Frame-Sync-Polarity-Interleave-Modes.png (file) |  |

166 KB | Ghalfacree | Higher-resolution version. | 2 |

| 10:02, 1 October 2015 | LMS6002D-Baseband-Data-Interface.png (file) |  |

121 KB | Ghalfacree | Higher-resolution version. | 2 |

| 10:01, 1 October 2015 | LMS6002D-LPF-Amplitude-Response-2.png (file) |  |

34 KB | Ghalfacree | Higher-resolution version. | 2 |

| 10:01, 1 October 2015 | LMS6002D-LPF-Amplitude-Response-1.png (file) |  |

34 KB | Ghalfacree | Higher-resolution version. | 2 |

| 10:01, 1 October 2015 | LMS6002D-PLL-Reference-Clock-Input-Buffer-AC-Coupled.png (file) |  |

95 KB | Ghalfacree | Higher-resolution version. | 2 |

| 10:00, 1 October 2015 | LMS6002D-PLL-Reference-Clock-Input-Buffer-DC-Coupled.png (file) |  |

95 KB | Ghalfacree | Higher-resolution version. | 2 |

| 10:00, 1 October 2015 | LMS6002D-PLL-Architecture.png (file) |  |

106 KB | Ghalfacree | Higher-resolution version. | 2 |

| 09:59, 1 October 2015 | LMS6002D-RX-Gain-Control-Architecture.png (file) |  |

109 KB | Ghalfacree | Higher-resolution version. | 2 |

| 09:59, 1 October 2015 | LMS6002D-TX-Gain-Control-Architecture.png (file) |  |

91 KB | Ghalfacree | Higher-resolution version. | 2 |

| 09:59, 1 October 2015 | LMS6002D-Functional-Block-Diagram.png (file) |  |

475 KB | Ghalfacree | Higher-resolution version. | 2 |

| 09:57, 1 October 2015 | LMS6002D-SPI-Read-Cycle-3-Wire.png (file) | 200 KB | Ghalfacree | Higher-resolution version. | 2 | |

| 09:56, 1 October 2015 | LMS6002D-SPI-Read-Cycle-4-Wire.png (file) | 230 KB | Ghalfacree | Higher-resolution version. | 4 | |

| 09:54, 1 October 2015 | LMS6002D-SPI-Write-Cycle.png (file) | 189 KB | Ghalfacree | Higher-resolution version. | 2 | |

| 16:32, 15 September 2015 | SNOWLeoSDR.jpg (file) |  |

125 KB | AndrewBack | 1 | |

| 16:09, 15 September 2015 | KiCAD footprints.png (file) |  |

321 KB | AndrewBack | 1 | |

| 15:21, 15 September 2015 | LMS7002M-1024w.jpg (file) |  |

95 KB | AndrewBack | 1 | |

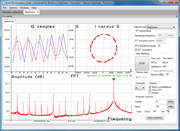

| 14:37, 15 September 2015 | LMS Suite FFTviewer.png (file) |  |

74 KB | AndrewBack | 1 | |

| 14:32, 15 September 2015 | LMS Suite LMS6002RxPLL.png (file) |  |

76 KB | AndrewBack | 1 | |

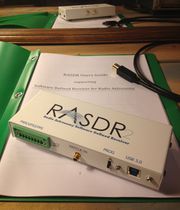

| 13:48, 15 September 2015 | Rasdr2-case-inside.jpg (file) |  |

687 KB | BogdanVacaliuc | Photograph of the inside of the RASDR2 showing the DigiRED+MyriadRF and mountings. | 1 |

| 13:45, 15 September 2015 | Rasdr2-case-montage-cropped.jpg (file) |  |

795 KB | BogdanVacaliuc | good first-impression of RASDR product, fitted in case design concept #1 (used for the 2015 loaner program) | 1 |

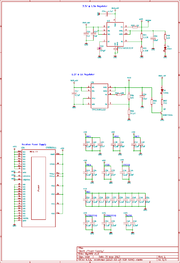

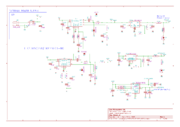

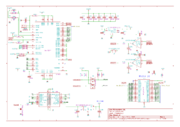

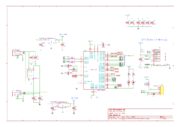

| 13:42, 15 September 2015 | Digired-clock-generator.png (file) |  |

56 KB | BogdanVacaliuc | page 5 of Digired schematic - transmit side cropped | 1 |

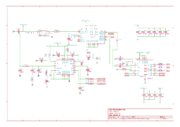

| 13:42, 15 September 2015 | Digired-power-supply.png (file) |  |

51 KB | BogdanVacaliuc | page 4 of Digired schematic - transmit side cropped | 1 |

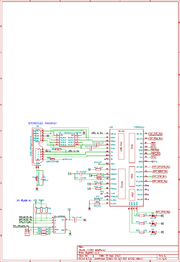

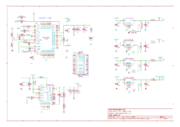

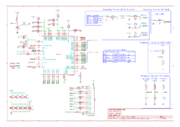

| 13:42, 15 September 2015 | Digired-usb3-interface.png (file) |  |

50 KB | BogdanVacaliuc | page 3 of Digired schematic - transmit side cropped | 1 |

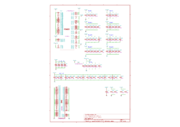

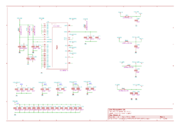

| 13:41, 15 September 2015 | Digired-digital-interface.png (file) |  |

38 KB | BogdanVacaliuc | page 2 of Digired schematic - transmit side cropped | 1 |

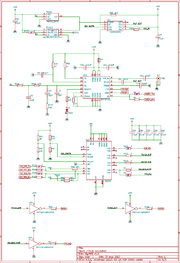

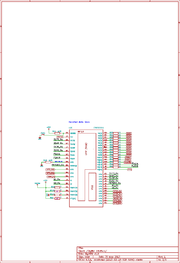

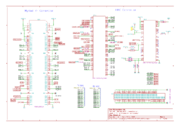

| 13:40, 15 September 2015 | Digired-connectors.png (file) |  |

62 KB | BogdanVacaliuc | page 1 of Digired schematic - transmit side cropped | 1 |

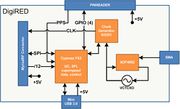

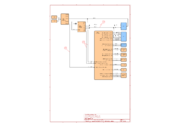

| 13:29, 15 September 2015 | 659x-Digired-Block-Diagram.jpg (file) |  |

83 KB | BogdanVacaliuc | DigiRED block diagram as used by RASDR | 1 |

| 20:33, 30 August 2015 | Myriad-RF Community Icon 167x70.jpg (file) | 5 KB | AndrewBack | 1 | ||

| 19:32, 20 August 2015 | LimeMicrosystems 167x70.jpg (file) |  |

5 KB | AndrewBack | 1 | |

| 15:36, 20 August 2015 | Myriad-RF Community Icon 167x111.jpg (file) | 8 KB | AndrewBack | 1 | ||

| 16:43, 18 August 2015 | Myriad-RF 167x65.jpg (file) |  |

8 KB | AndrewBack | Myriad-RF logo for navbox template | 1 |

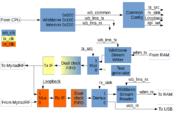

| 17:20, 22 July 2015 | Myriad-RF-IF-Block-Diagram.png (file) |  |

148 KB | Ghalfacree | STREAM Board Myriad-RF Interface Block Diagram. | 1 |

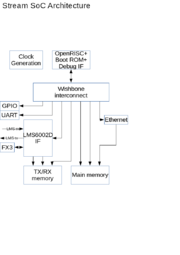

| 16:58, 22 July 2015 | STREAM-OpenRISC-Block-Diagram.png (file) |  |

67 KB | Ghalfacree | Block diagram for the STREAM OpenRISC project. | 1 |

| 16:29, 22 July 2015 | STREAM-Board-GPIF-II.jpg (file) |  |

20 KB | Ghalfacree | STREAM Board GPIF II-related connections between FX3 and FPGA. | 1 |

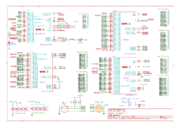

| 15:35, 22 July 2015 | STREAM-Schematics-15.png (file) |  |

721 KB | Ghalfacree | STREAM Schematics Page 15, FPGA Banks 1-4. | 1 |

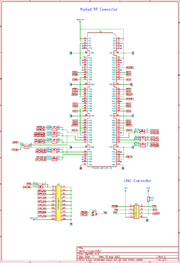

| 15:34, 22 July 2015 | STREAM-Schematics-14.png (file) |  |

467 KB | Ghalfacree | STREAM Schematics Page 14, FMC and Myriad-RF Connectors. | 1 |

| 15:34, 22 July 2015 | STREAM-Schematics-13.png (file) |  |

318 KB | Ghalfacree | STREAM Schematics Page 13, FPGA Power Distribution. | 1 |

| 15:33, 22 July 2015 | STREAM-Schematics-12.png (file) |  |

205 KB | Ghalfacree | STREAM Schematics Page 12, Clocks Block Diagram. | 1 |

| 15:33, 22 July 2015 | STREAM-Schematics-11.png (file) |  |

350 KB | Ghalfacree | STREAM Schematics Page 11, Board Power Supply 2. | 1 |

| 15:32, 22 July 2015 | STREAM-Schematics-10.png (file) |  |

264 KB | Ghalfacree | STREAM Schematics Page 10, Board Power Supply 1. | 1 |

| 15:32, 22 July 2015 | STREAM-Schematics-9.png (file) |  |

237 KB | Ghalfacree | STREAM Schematics Page 9, USB 3.0 Power Supply. | 1 |

| 15:31, 22 July 2015 | STREAM-Schematics-8.png (file) |  |

248 KB | Ghalfacree | STREAM Schematics Page 8, Clocks. | 1 |

| 15:31, 22 July 2015 | STREAM-Schematics-7.png (file) |  |

402 KB | Ghalfacree | STREAM Schematics Page 7, Ethernet. | 1 |

| 15:30, 22 July 2015 | STREAM-Schematics-6.png (file) |  |

436 KB | Ghalfacree | STREAM Schematics Page 6, Peripherals. | 1 |

| 15:29, 22 July 2015 | STREAM-Schematics-5.png (file) |  |

296 KB | Ghalfacree | STREAM Schematics Page 5, USB 2.0 Host. | 1 |