STREAM Communications: Difference between revisions

Ghalfacree (talk | contribs) (Initial page creation.) |

Ghalfacree (talk | contribs) m (Removed excess carriage return.) |

||

| Line 227: | Line 227: | ||

|} | |} | ||

Check application note AN65974 from Cypress, "Design Example 1: Interfacing an Xilinx FPGA to FX3’s Synchronous Slave FIFO Interface," for a more detailed explanation on how to implement the StreamIN interface between FX3 and FPGA. | Check application note AN65974 from Cypress, "Design Example 1: Interfacing an Xilinx FPGA to FX3’s Synchronous Slave FIFO Interface," for a more detailed explanation on how to implement the StreamIN interface between FX3 and FPGA. | ||

===See also=== | ===See also=== | ||

Revision as of 15:55, 22 July 2015

IQ sample data formats for PC and FX3 communications

Uncompressed data format

Stream board samples uses 1 bit for I or Q channel selection and 12 bits for amplitude. One pair of I and Q samples makes up one frame. Each frame is transferred using 4 bytes as shown below.This data format is used for uploading and downloading samples.

| Buffer byte index | Data (8-bits) | Frame |

|---|---|---|

| 0 | [7:0] I0 LSB | 0 |

| 1 | 0x00 + [3:0] I0 MSB | |

| 2 | [7:0] Q0 LSB | |

| 3 | 0x10 + Q0 MSB | |

| 4 | [7:0] I1 LSB | 1 |

| 5 | 0x00 + [3:0] I1 MSB | |

| 6 | [7:0] Q1 LSB | |

| 7 | 0x10 + Q1 MSB | |

| ... | ... | ... |

Stream board PC and FX3 communications

Stream board can be connected to the PC by USB 2.0 or USB 3.0. The software can perform SPI registers writing and reading operations over USB device’s control endpoints using LMS64C control protocol. The control endpoints should be configured as shown below.

| Field | In Endpoint | Out Endpoint |

|---|---|---|

| Request Code | 0xC0 | 0xC1 |

| Value | 0x000 | 0x000 |

| Index | 0x000 | 0x000 |

The following commands are supported in Stream board bridge MCU (FX3):

- CMD_GET_INFO

- CMD_LMS_RST

- CMD_SI5351_WR

- CMD_SI5351_RD

- CMD_LMS6002_WR

- CMD_LMS6002_RD

- CMD_LMS7002_WR

- CMD_LMS7002_RD

- CMD_ADF4002_WR

- LMS_BRDSPI16_WR

- LMS_BRDSPI16_RD

- CMD_ALTERA_FPGA_GW_WR

Getting board information

Send a CMD_GET_INFO command to the bridge MCU to get information about the hardware. Stream board information is returned by MCU as shown below:

| Field | Value |

|---|---|

| FW_ver | 2 |

| Dev_type | 8 |

| Protocol_ver | 1 |

| HW_ver | 2 |

| EXP_ID | 0 |

Resetting LMS chip

Send a CMD_LMS_RST command to the bridge MCU to to reset the LMS chip.

Communicating with LMS transceivers

Various expansion boards may be connected to the Stream board. Expansion boards may be populated with LMS6002D or LMS7002M transceivers. The commands CMD_LMS6002_WR, CMD_LMS6002_RD, CMD_LMS7002_WR and CMD_LMS7002_RD are designed to set-up and read set-up data to these transceivers.

Communicating with Si5351

The Stream board has a Si5351 clock synthesiser onboard. The commands CMD_SI5351_WR and CMD_SI5351_RD are dedicated for Si5351 clock synthesiser set-up.

Communicating with ADF4002

The Stream board has an ADF4002 PLL onboard. The command CMD_ADF4002_WR is dedicated for ADF4002 set-up. It is not possible to read the configuration data from ADF4002.

FPGA modules setup

The FPGA hardware on the Stream board is controlled by 16 bit memory registers, which can be read or written by using the LMS64C data protocol, CMD_BRDSPI16_WR and CMD_BRDSPI16_RD commands. The SPI registers are shown below.

| Address (15 bits) | Bits | Description |

|---|---|---|

| 0x0005 | 15-5 | Unused |

| 4 | CH_SEL: Selects Rx channel for streaming to FX3 | |

| 0 - DIQ1 (default) | ||

| 1 - DIQ2 | ||

| 3 | STREAM_RXDSRC: Selects Rx data source: | |

| 0 - NCO (default) | ||

| 1 - ADC | ||

| 2 | STREAM_RXEN: Enables data streaming from FPGA to FX3 | |

| 0 - Disabled (default) | ||

| 1 - Enabled | ||

| 1 | STREAM_TXEN: Enables data streaming from RAM | |

| 0 - Disabled | ||

| 1 - Enabled (default) | ||

| 0 | STREAM_LOAD: Enables data loading | |

| 0 - Enabled (default) | ||

| 1 - Disabled | ||

| Default: 0000000 00000010 | ||

FPGA programming

FPGA programming is performed by sending data to the USB device’s control end point. Data needs to be encapsulated in LMS64C packet, using the CMD_ALTERA_FPGA_GW_WR command.

IQ sample writing

IQ sample writing is performed by sending data to the USB device’s bulk end point, which has the address 0x01. Before that, the Stream board has to be configured to accept incoming data. The general steps for IQ sample writing are:

- Enable STREAM_LOAD and disable STREAM_TXEN, STREAM_RXEN.

- Transfer sample data to USB Endpoint whose address is 0x01. Sample writing can be done either in one transaction, or several successive transactions.

- Disable STREAM_LOAD and enable STREAM_TXEN.

IQ sample reading

IQ sample reading is performed by reading data from the USB device’s bulk end point, which has address 0x81. Before that, the Stream board has to be configured to send out data samples. The general steps for IQ sample reading are:

- Enable STREAM_RXEN.

- Read data samples from USB Endpoint whose address is 0x81. Reading can be repeated indefinitely.

- After reading is done, disable STREAM_RXEN.

Stream board FX3 and FPGA communications

Introduction

Communication between the FX3 USB microcontroller and FPGA are performed using the GPIF II interface configured as slave FIFO with a 16 bit width data bus. Implementation is based on the AN65974 application note from Cypress.

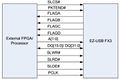

FX3 and FPGA GPIF II related connections are as shown in the below image.

-

FX3 and FPGA GPIF II-related connections

Detailed description of the signals is provided below.

| Signal Name | Schematic Signal Name | FPGA Pin | SIgnal Description |

|---|---|---|---|

| SLCS# | FX3_CTL[0] | L7 | Chip select signal for the Slave FIFO interface. It must be asserted to access Slave FIFO. |

| SLWR# | FX3_CTL[1] | M4 | Write strobe for the Slave FIFO interface. It must be asserted to perform write transfers to the Slave FIFO. |

| SLRD# | CTL[3] | M7 | Read strobe for the Slave FIFO interface. It must be asserted to perform read transfers from the Slave FIFO. |

| SLOE# | FX3_CTL[2] | M8 | Output enable signal. It causes the data bus out of the Slave FIFO interface to be driven by FX3. It must be asserted to perform read transfers from the Slave FIFO. |

| FLAGA, FLAGB, FLAGC, FLAGD | FX3_CTL[4], FX3_CTL[5], FX3_CTL[6], FX3_CTL[8] | M5, P7, M3, N8 | Flag outputs from FX3. The flags indicate the availability of an FX3 socket. FLAGA, FLAGB are used for Slave FIFO write operations and FLAGC, FLAGD are used for Slave FIFO read operations. |

| A[1:0] | FX3_CTL[11], FX3_CTL[12] | N7, N5 | 2-bit address bus for Slave FIFO. |

| DQ[15:0] | FX3_DQ[0..15] | R2, R1, V2, V1, U2, U1, R5, T3, P4, P5, N2, P2, P1, M1, N1, P3 | 16-bit address bus for Slave FIFO. |

| PKTEND# | FX3_CTL[7] | L6 | Assert to write a short or zero-length packet to the Slave FIFO. |

| PCLK | FX3_PCLK | M2 | Slave FIFO interface clock. |

StreamIN data transfers (from FPGA to FX3)

StreamIN transmits the data from the FPGA to FX3 and then to the PC. To implement StreamIN data transfers some signals, listed in GPIF II-related connections, may be connected to the high or low level as shown below; please note that the active (asserted) signal level is low.

| Signal Name | Connect To | Explanation |

|---|---|---|

| SLCS# | Low | Assert to access Slave FIFO. |

| SLWR# | From FPGA data write logic. | Assert to perform write transfers to Slave FIFO. |

| SLRD# | High | Read strobe for the Slave FIFO interface, not used for StreamIN transfers. |

| SLOE# | High | Data are driven from the FPGA |

| FLAGA | To FPGA data write logic. | FLAGA indicates the Slave FIFO is full when asserted. |

| FLAGB | To FPGA data write logic. | FLAGB is a partial flag and indicates Slave FIFO water level. Becomes asserted when there is room for two words to write. |

| FLAGC | To FPGA data write logic. | Not used. |

| FLAGD | To FPGA data write logic. | Not used. |

| A[1:0] | Low, Low | Two-bit address bus of Slave FIFO, "00". |

| DQ[15:0] | From FPGA data write logic. | 16-bit data bus of Slave FIFO. |

| PKTEND# | High | Do not use the short packet or zero-length packet feature. |

| PCLK | From FPGA. | Slave FIFO interface clock, provided from FPGA. |

Check application note AN65974 from Cypress, "Design Example 1: Interfacing an Xilinx FPGA to FX3’s Synchronous Slave FIFO Interface," for a more detailed explanation on how to implement the StreamIN interface between FX3 and FPGA.

StreamOUT data transfers (from FX3 to FPGA)

StreamOUT transmits the data from the PC to FX3 and then to the FPGA. To implement StreamOUT data transfers some signals, listed in GPIF II-related connections, may be connected to the high or low level as shown below; please note that the active (asserted) signal level is low.

| Signal Name | Connect To | Explanation |

|---|---|---|

| SLCS# | Low | Assert to access Slave FIFO. |

| SLWR# | From FPGA data write logic. | Write strobe for the Slave FIFO interface; not used for StreamOUT transfers. |

| SLRD# | High | Assert to perform read transfers from the Slave FIFO. |

| SLOE# | High | Assert when data are driven from FX3. |

| FLAGA | To FPGA data write logic. | Not used. |

| FLAGB | To FPGA data write logic. | Not used. |

| FLAGC | To FPGA data write logic. | FLAGC indicates the Slave FIFO is empty when asserted. |

| FLAGD | To FPGA data write logic. | FLAGD is a partial flag and indicates Slave FIFO water level. Becomes asserted when there are 0 not read words. |

| A[1:0] | Low, Low | Two-bit address bus of Slave FIFO, "11". |

| DQ[15:0] | From FPGA data write logic. | 16-bit data bus of Slave FIFO. |

| PKTEND# | High | Do not use the short packet or zero-length packet feature. |

| PCLK | From FPGA. | Slave FIFO interface clock, provided from FPGA. |

Check application note AN65974 from Cypress, "Design Example 1: Interfacing an Xilinx FPGA to FX3’s Synchronous Slave FIFO Interface," for a more detailed explanation on how to implement the StreamIN interface between FX3 and FPGA.