LimeSDR-USB hardware description: Difference between revisions

Jump to navigation

Jump to search

No edit summary |

No edit summary |

||

| Line 21: | Line 21: | ||

** 116 embedded 18x18 multipliers | ** 116 embedded 18x18 multipliers | ||

** 4 PLLs | ** 4 PLLs | ||

* '''FPGA Configuration''' | |||

** JTAG mode configuration | |||

** Active serial mode configuration | |||

** Possibility to update FPGA gateware by using FX3 (USB) | |||

* '''Memory Devices''' | |||

** 2x 1Gbit (64M x 16) DDR2 SDRAM | |||

** 4Mbit flash for FX3 firmware | |||

** 16Mbit flash for FPGA gateware | |||

** 2 x 128K (16K x 8) EEPROMs for LMS MCU firmware, LMS MCU data | |||

** 1 x 64K (8K x 8) EEPROM for FX3 data | |||

* '''Connections''' | |||

** microUSB3.0 (type B) connector or USB3.0 (type A) plug | |||

** Coaxial RF (U.FL) connectors | |||

** FPGA GPIO headers (0.05” pitch) | |||

** FPGA and FX3 JTAG connectors (0.05” pitch) | |||

** 6..12V DC power jack and pinheader | |||

** Fan connector (3.3V) | |||

* '''Clock System''' | |||

** 30.72MHz VCTCXO (precision: ±1 ppm initial, ±4 ppm stable). | |||

** Possibility to lock VCTCXO to external clock or tune VCTCXO by onboard DAC | |||

** Programmable clock generator for the FPGA reference clock input or LMS PLLs | |||

** '''Board Size''' 60mm x 100mm (2.36” x 3.94”) | |||

Revision as of 12:46, 23 August 2017

LimeSDR-USB Board Key Features

The LimeSDR-USB development board provides a hardware platform for developing and prototyping high-performance and logic-intensive digital and RF designs using Altera’s Cyclone IV FPGA and Lime Microsystems transceiver.

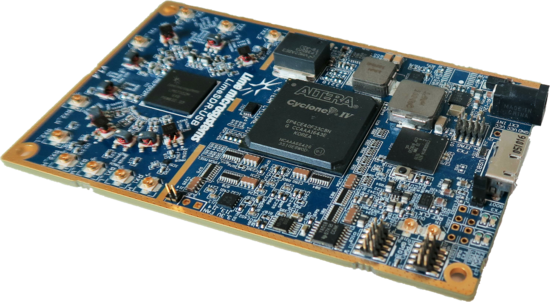

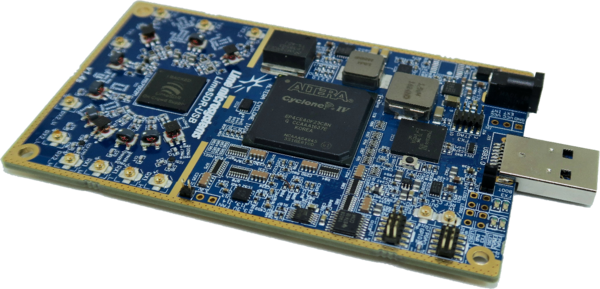

The LimeSDR-USB has two different USB connector versions. LimeSDR-USB 1v4 is micro USB type B connector (socket) based, as shown in Figure 1. LimeSDR-USB 1v4s is a USB type A connector (plug) based, as shown in Figure 2.

LimeSDR-USB board features:

- USB Interface

- Cypress FX3 Super Speed USB 3rd generation controller

- FPGA Features

- Cyclone IV EP4CE40F23C8N device in 484-pin FPGA

- 39’600 logic elements

- 1134 Kbits embedded memory

- 116 embedded 18x18 multipliers

- 4 PLLs

- FPGA Configuration

- JTAG mode configuration

- Active serial mode configuration

- Possibility to update FPGA gateware by using FX3 (USB)

- Memory Devices

- 2x 1Gbit (64M x 16) DDR2 SDRAM

- 4Mbit flash for FX3 firmware

- 16Mbit flash for FPGA gateware

- 2 x 128K (16K x 8) EEPROMs for LMS MCU firmware, LMS MCU data

- 1 x 64K (8K x 8) EEPROM for FX3 data

- Connections

- microUSB3.0 (type B) connector or USB3.0 (type A) plug

- Coaxial RF (U.FL) connectors

- FPGA GPIO headers (0.05” pitch)

- FPGA and FX3 JTAG connectors (0.05” pitch)

- 6..12V DC power jack and pinheader

- Fan connector (3.3V)

- Clock System

- 30.72MHz VCTCXO (precision: ±1 ppm initial, ±4 ppm stable).

- Possibility to lock VCTCXO to external clock or tune VCTCXO by onboard DAC

- Programmable clock generator for the FPGA reference clock input or LMS PLLs

- Board Size 60mm x 100mm (2.36” x 3.94”)