LimeNET-Micro v2.1 hardware description: Difference between revisions

| Line 352: | Line 352: | ||

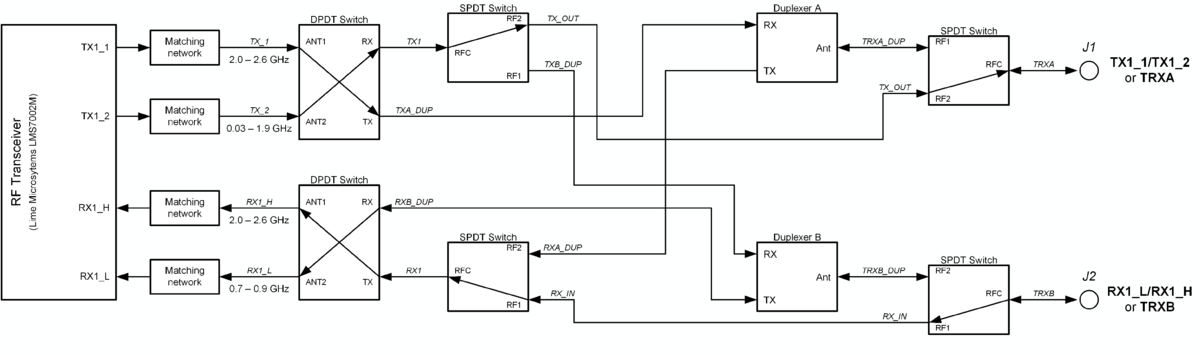

For RF path description connected to Lime Microsystems RF transceiver LMS7002M refer to Figure 5. There are two DPDT switches which selects between LMS7002M RF ports and matching networks. Optionally there can be duplexers fitted onboard and path with duplexers or without them are selected with SPDT switches. | For RF path description connected to Lime Microsystems RF transceiver LMS7002M refer to Figure 5. There are two DPDT switches which selects between LMS7002M RF ports and matching networks. Optionally there can be duplexers fitted onboard and path with duplexers or without them are selected with SPDT switches. | ||

[[File:LimeNET-Micro_2.1_LMS7002M_RF_path.png|thumb|center| | [[File:LimeNET-Micro_2.1_LMS7002M_RF_path.png|thumb|center|1200px|Figure 5. LMS7002M RF path ]] | ||

Revision as of 15:36, 20 March 2019

LimeNET-Micro Board Key Features

LimeNET Micro makes deploying wireless networks more accessible than ever before, by extending the LimeNET line of integrated hardware solutions via an ultra-low cost platform that is capable of supporting narrowband systems, such as GSM and IoT wireless standards, in a stand-alone configuration.

LimeNET-Micro board features:

- RF transceiver

- Lime Microsystems LMS7002M

- Raspberry Pi

- DDR2 SODIMM socket for raspberry Pi CM3(L)

- 2x downstream USB 2.0 ports

- Upstream Micro-USB for USB boot of Compute Module

- 3.5mm analog audio, composite video output

- Ethernet + active PoE (RJ45) connector

- Ribbon cable camera and display connectors

- HDMI connector

- External UART connector

- uSD card slot

- USB2.0 HUB and 10/100 Ethernet controller

- SDIO Wi-Fi module

- Jumper for Raspberry boot mode selection

- FPGA Features

- Intel MAX10 10M16SAU169C8 device in 169-pin UBGA

- 16K logic elements

- 549 Kbits embedded memory (M9K) and 2368 Kbits of user Flash Memory

- 45 embedded 18x18 multipliers

- 1 PLLs

- FPGA Configuration

- JTAG mode configuration

- USB Controller

- FTDI FT601 USB to FIFO interface bridge chip (connects FPGA to USB2.0 HUB)

- Memory Devices

- 4Mbit FLASH (for FPGA data)

- 2x 128Kbit (16K x 8) EEPROM (for LMS MCU firmware and FPGA data)

- Other Devices

- Temperature sensor

- Crypto Authentication Device

- GNSS receiver

- Connections

- 2 x coaxial RF (SMA) connectors

- SMA connectors for reference clock IN/OUT, GNSS and Wi-Fi antennas

- 5V DC power jack

- 5V header for powering external devices

- Fan header

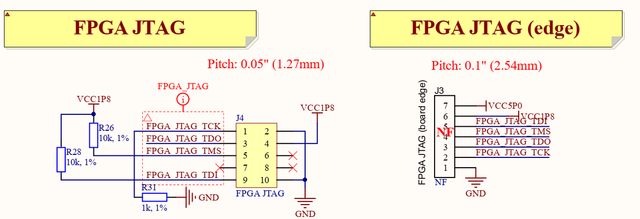

- FPGA JTAG connectors (0.05” pitch and side connector)

- Backup battery connector for GNSS receiver

- Clock System

- 30.72MHz VCOCXO:

- Frequency calibration ±0.5ppm;

- Frequency stability over temperature in still air ±20ppb;

- Frequency slope ΔF/ΔT in still air ±1.2ppb/°C

- Possibility to tune VCOCXO by onboard DAC

- Possibility to use GNSS PPS signal as a reference when tuning VCOCXO frequency

- 30.72MHz VCOCXO:

- User I/O

- GPIO header (0.05” pitch) connected to FPGA

- 5X dual color (RG) LEDs connected to FPGA

- Push button connected to FPGA

- Buzzer connected to FPGA

- Board Size: without connectors 125mm x 65mm (4.92” x 2.56”)

For more information on the following topics, refer to the respective documents:

- FT601 controller resources [link]

- MAX10 device family, refer to Intel documentation [link]

- LMS7002M transceiver resources [link]

Board Overview

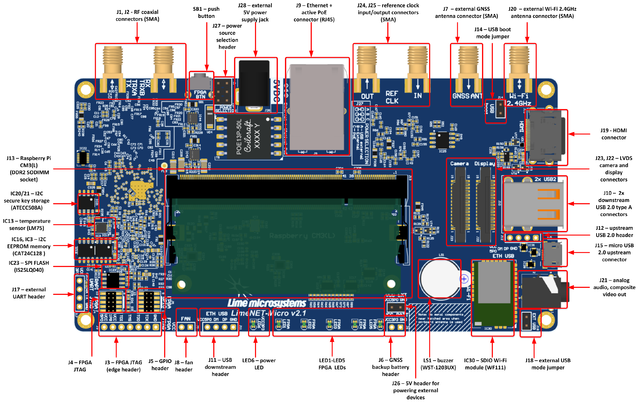

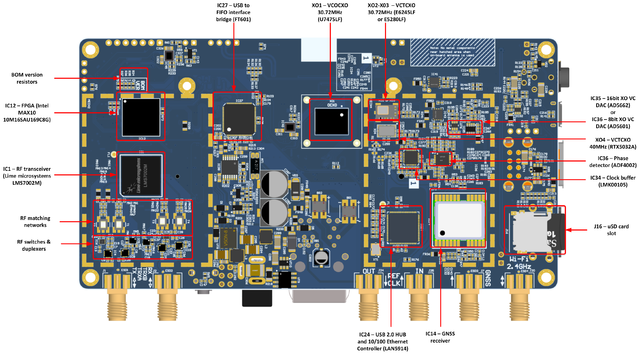

LimeNET-Micro board version 2.1 picture with highlighted major components and connections presented in Figure 1 and Figure 2. Lime Microsystems LMS7002M RF transceiver and Intel MAX10 FPGA can be found on bottom side of board, DDR2 SODIMM socket for Raspberry PI Compute module is placed on top side. There are three connector types – data and debugging (USB2.0, FPGA GPIO, Ethernet and JTAG), power (DC jack and external supply pinheader), RF (clock source output, GNSS antenna and time pulse output, RF transmit and receive ports). LimeNET-Micro 2.1 board comes in three versions and each version differs in components which are fitted on board (BOM – Bill Of Material). BOM version can be determined from resistors R34, R35, R36, R37 fitted on board (see Figure 2 “BOM version resistors” and Table 1 for version description).

| BOM_VER | R34 | R35 | R36 | R37 | Comment |

|---|---|---|---|---|---|

| 0 | Fitted | Fitted | Fitted | Fitted | Lime (full version) |

| 1 | NF | Fitted | Fitted | Fitted | SDR (without duplexers and WiFi module) |

| 2 | Fitted | NF | Fitted | Fitted | GSM (with duplexers, without PoE, audio and video) |

Board components description listed in the Table 2 and Table 3.

| Featured devices | ||

|---|---|---|

| Board Reference | Type | Description |

| IC1 | RF transceiver | Lime Microsystems LMS7002M |

| IC14 | GNSS module | GNSS receiver |

| IC12 | FPGA | Intel MAX10, 10M16SAU169C8G, 169-UBGA |

| IC24 | USB 2.0 HUB | Microchip Technology LAN9514 USB 2.0 Hub and 10/100 Ethernet Controller |

| IC27 | USB to FIFO | FTDI FT601, USB to FIFO interface bridge |

| IC30 | Wi-Fi | SDIO Wi-Fi module (WF111) |

| Miscellaneous devices onboard | ||

| IC13 | IC | Temperature sensor LM75 |

| IC20/21 | IC | I2C secure key storage ATECC508A |

| Configuration, Status and Setup Elements | ||

| J3 | JTAG chain pin header | FPGA programming pin header for Altera USB-Blaster download cable, side connection. |

| J4 | JTAG chain pin header | FPGA programming pin header for Altera USB-Blaster download cable, 0.05” pitch |

| LED1,

LED2, LED3, LED4, LED5 |

Red-green status LEDs | User defined FPGA indication. |

| LED6 | Red-green status LEDs | VCC3P3 power rail indications |

| LS1 | Buzzer | Buzzer (WST-1203UX), connected to FPGA. |

| J14 | Jumper | USB boot mode jumper |

| J18 | Jumper | External USB mode jumper |

| J27 | Jumper | Power source selection |

| General User Input/Output | ||

| J5 | Pin header | 8 FPGA GPIOs plus 2 power pins, 0.05” pitch |

| SB1 | Push button | Push button connected to FPGA |

| Memory Devices | ||

| IC3, IC16 | EEPROM | 128K (16K x 8) EEPROM connected to FPGA and LMS7002M |

| IC23 | Flash memory | 4Mbit FLASH memory connected to FPGA |

| Communication Ports and interfaces | ||

| J9 | RJ45 connector | Ethernet + active PoE connector |

| J10 | USB2.0 connector | 2x downstream USB2.0 type A connectors |

| J11 | Header | USB downstream header |

| J12 | Header | Upstream USB2.0 header |

| J13 | Socket | DDR2 SODIMM socket for Raspberry Pi CM3(L) |

| J15 | USB2.0 connector | microUSB2.0 upstream connector |

| J17 | Header | External UART header |

| J19 | Connector | HDMI connector for display |

| J22 | Connector | LVDS connector for display |

| J23 | Connector | LVDS connector for camera |

| Clock Circuitry | ||

|---|---|---|

| Board Reference | Type | Description |

| XO1 | VCOCXO | 30.72 MHz voltage-controlled crystal oscillator used as a reference clock. |

| XO2 | VCTCXO | 30.72 MHz voltage-controlled, temperature compensated crystal oscillator used as a reference clock. |

| XO3 | VCTCXO | 30.72 MHz voltage-controlled, temperature compensated crystal oscillator used as a reference clock. (Not fitted by default) |

| XO4 | VCTCXO | 40.0 MHz voltage-controlled, temperature compensated crystal oscillator used as a reference clock. |

| IC35 OR IC37 | IC | Analog devices 16bit AD5662 or 8bit AD5601 Digital-to-analog converter for reference clock voltage control |

| IC36 | IC | Phase detector (ADF4002) |

| J25 | SMA connector | Reference clock input |

| J24 | SMA connector | Reference clock output |

| RF connectors | ||

| J1 | SMA connector | Transmit port or TRXA channel in duplex mode |

| J2 | SMA connector | Receive port or TRXB channel in duplex mode |

| J7 | SMA connector | GNSS module antenna connector |

| J20 | SMA connector | Antenna connector for Wi-Fi module |

| Power Supply | ||

| J28 | DC input jack | External 5V DC power supply input |

| J26 | Pin header | 5V DC power supply output header and main internal power rail |

| J6 | Pin header | Backup battery connection header for GNSS module. Typical 3.0V (follow recommendation in fitted GNSS module datasheet) |

| Other | ||

| J16 | Card slot | uSD card slot for Raspberry Pi boot |

| J11 | Header | Fan connection header |

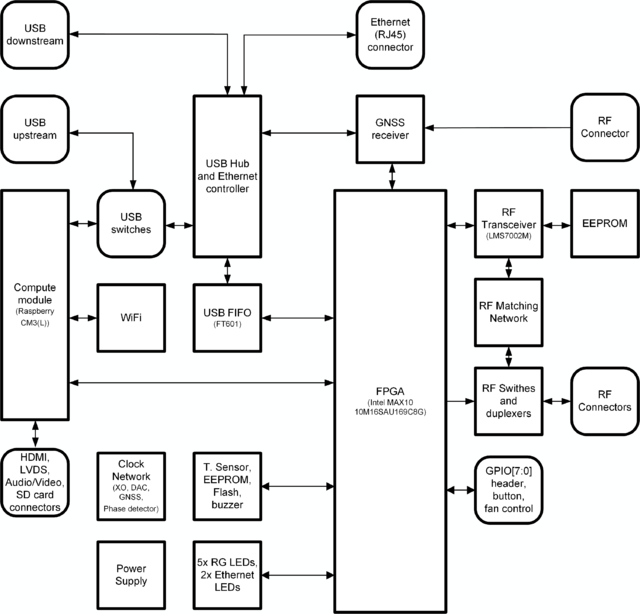

LimeNET-Micro board architecture

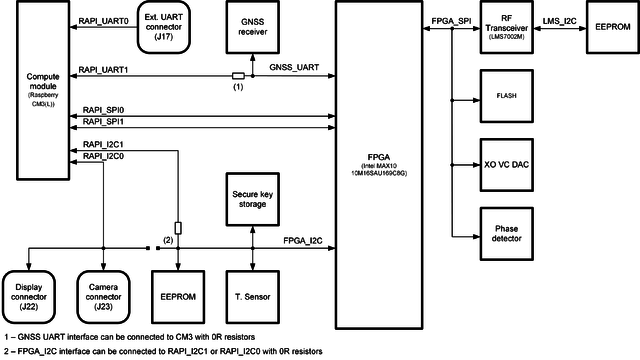

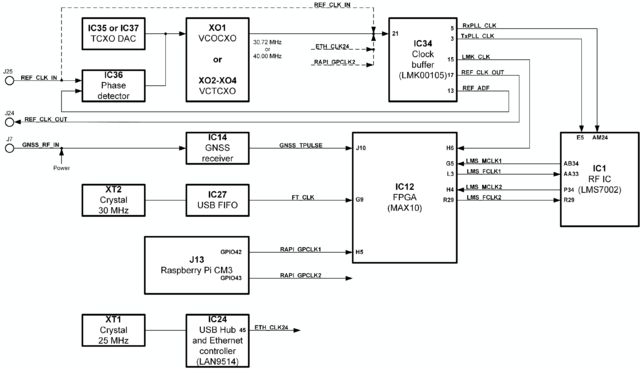

Board periphery can be divided in two groups – FPGA controlled periphery and Raspberry controlled periphery. Intel MAX10 FPGA acts as a glue logic between onboard periphery such as LMS7002M RF transceiver, FT601 USB-to-FIFO IC and Raspberry CM3. Due to FPGA reprogrammable nature additional logic can be implemented also. Raspberry CM3(L) can be used to implement various applications. The block diagram for LimeNET-Micro board is presented in Figure 4.

RF transceiver

The LMS7002M is a fully-integrated, multi-band, multi-standard RF transceiver that is highly programmable. It combines Low Noise Amplifiers (RXLNA), TX Power Amplifier Drivers (TXPAD) receiver/transmitter (RX/TX) mixers, RX/TX filters, synthesizers, RX gain control, TX power control, analogue-to-digital and digital-to-analogue converters (ADC/DACs) and has been designed to require very few external components.

For RF path description connected to Lime Microsystems RF transceiver LMS7002M refer to Figure 5. There are two DPDT switches which selects between LMS7002M RF ports and matching networks. Optionally there can be duplexers fitted onboard and path with duplexers or without them are selected with SPDT switches.

LMS7002 is connected to Intel MAX10 FPGA. The interface and control signals are described below:

- Digital Interface Signals: LMS7002M is using data bus LMS_DIQ1_D[11:0] and LMS_DIQ2_D[11:0], LMS_ENABLE_IQSEL1 and LMS_ENABLE_IQSEL2, LMS_FCLK1 and LMS_FCLK2, LMS_MCLK1 and LMS_MCLK2 signals to transfer data to/from FPGA. Indexes 1 and 2 indicate transceiver digital data PORT-1 or PORT-2. Any of these ports can be used to transmit or receive data. By default, PORT-1 is selected as transmit port and PORT-2 is selected as receiver port. The FCLK# is input clock and MCLK# is output clock for LMS7002M transceiver. TXNRX signals sets ports directions. For LMS7002M interface timing details refer to LMS7002M transceiver datasheet page 12-13. [link]

- LMS Control Signals: these signals are used for optional functionality:

- LMS_RXEN, LMS_TXEN – receiver and transmitter enable/disable signals

- LMS_RESET – LMS7002M reset;

- SPI Interface: LMS7002M transceiver is configured via 4-wire SPI interface; FPGA_SPI0_SCLK, FPGA_SPI0_MOSI, FPGA_SPI0_MISO, FPGA_SPI0_LMS_SS. The SPI interface controlled from FPGA.

- LMS I2C Interface: Connected to LMS EEPROM.

For connection details see Table 4.

| Chip pin (IC1) | Chip reference (IC1) | Schematic signal name | FPGA pin | FPGA I/O standard | Description |

|---|---|---|---|---|---|

| AM24 | xoscin_rxx | RxPLL_CLK | NC | 3.3V | Connected to 30.72 MHz clock |

| P34 | MCLK2 | LMS_MCLK2 | H4 | 3.3V | |

| R29 | FCLK2 | LMS_FCLK2 | M3 | 3.3V | |

| U31 | TXNRX2 | LMS_TXNRX2 | C4 | 3.3V | |

| V34 | RXEN | LMS_RXEN | - | - | Connected to shift register |

| R33 | ENABLE_IQx | LMS_ENABLE_IQSEL2 | N3 | 3.3V | |

| H30 | DIQ2_D0 | LMS_DIQ2_D0 | M1 | 3.3V | |

| J31 | DIQ2_D1 | LMS_DIQ2_D1 | L5 | 3.3V | |

| K30 | DIQ2_D2 | LMS_DIQ2_D2 | K2 | 3.3V | |

| K32 | DIQ2_D3 | LMS_DIQ2_D3 | M2 | 3.3V | |

| L31 | DIQ2_D4 | LMS_DIQ2_D4 | M4 | 3.3V | |

| K34 | DIQ2_D5 | LMS_DIQ2_D5 | J1 | 3.3V | |

| M30 | DIQ2_D6 | LMS_DIQ2_D6 | L2 | 3.3V | |

| M32 | DIQ2_D7 | LMS_DIQ2_D7 | K1 | 3.3V | |

| N31 | DIQ2_D8 | LMS_DIQ2_D8 | N4 | 3.3V | |

| N33 | DIQ2_D9 | LMS_DIQ2_D9 | J2 | 3.3V | |

| P30 | DIQ2_D10 | LMS_DIQ2_D10 | L4 | 3.3V | |

| P32 | DIQ2_D11 | LMS_DIQ2_D11 | N2 | 3.3V | |

| E5 | xoscin_txx | TxPLL_CLK | NC | 3.3V | Connected to 30.72 MHz clock |

| AB34 | MCLK1 | LMS_MCLK1 | G5 | 3.3V | |

| AA33 | FCLK1 | LMS_FCLK1 | L3 | 3.3V | |

| V32 | TXNRX1 | LMS_TXNRX1 | N6 | 3.3V | |

| U29 | TXEN | LMS_TXEN | - | - | Connected to shift register |

| 1Y32 | ENABLE_IQx | LMS_ENABLE_IQSEL1 | N7 | 3.3V | |

| AG31 | DIQ1_D0 | LMS_DIQ1_D0 | N12 | 3.3V | |

| AF30 | DIQ1_D1 | LMS_DIQ1_D1 | M12 | 3.3V | |

| AF34 | DIQ1_D2 | LMS_DIQ1_D2 | N11 | 3.3V | |

| AE31 | DIQ1_D3 | LMS_DIQ1_D3 | L10 | 3.3V | |

| AD30 | DIQ1_D4 | LMS_DIQ1_D4 | N9 | 3.3V | |

| AC29 | DIQ1_D5 | LMS_DIQ1_D5 | M13 | 3.3V | |

| AE33 | DIQ1_D6 | LMS_DIQ1_D6 | M10 | 3.3V | |

| AD32 | DIQ1_D7 | LMS_DIQ1_D7 | N10 | 3.3V | |

| AC31 | DIQ1_D8 | LMS_DIQ1_D8 | M8 | 3.3V | |

| AC33 | DIQ1_D9 | LMS_DIQ1_D9 | M9 | 3.3V | |

| AB30 | DIQ1_D10 | LMS_DIQ1_D10 | K6 | 3.3V | |

| AB32 | DIQ1_D11 | LMS_DIQ1_D11 | K7 | 3.3V | |

| U33 | CORE_LDO_x | LMS_CORE_LDO_EN | - | - | Connected to shift register |

| E27 | RESET | LMS_RESET | - | - | Connected to shift register |

| D28 | SEN | FPGA_SPI_LMS_SS | J5 | 3.3V | SPI interface |

| C29 | SCLK | FPGA_SPI_SCLK | M5 | 3.3V | SPI interface |

| F30 | SDIO | FPGA_SPI_MOSI | K5 | 3.3V | SPI interface |

| F28 | SDO | FPGA_SPI_MISO | N5 | 3.3V | SPI interface |

| D26 | SDA | LMS_I2C_SDA | - | - | Connected to EEPROM |

| C27 | SCL | LMS_I2C_SCL | - | - | Connected to EEPROM |

Raspberry Pi Compute Module 3

LimeNET-Micro board has DDR2 SODIMM socket which is dedicated only for Raspberry Pi Compute Module 3 (CM3 OR CM3L) connection. CM3 module has various periphery and FPGA connected to it. For detailed connection between CM3 and FPGA see Table 5.

| Conn. pin | Schematic signal name | FPGA pin | I/O standard |

|---|---|---|---|

| 35 | RAPI_SPI0_SCLK | F13 | 3.3V |

| 33 | RAPI_SPI0_MOSI | M11 | 3.3V |

| 29 | RAPI_SPI0_MISO | K8 | 3.3V |

| 27 | RAPI_SPI0_CE0 | E13 | 3.3V |

| 71 | RAPI_SPI1_SCLK | G10 | 3.3V |

| 69 | RAPI_SPI1_MOSI | K13 | 3.3V |

| 65 | RAPI_SPI1_MISO | L11 | 3.3V |

| 63 | RAPI_SPI1_CE0 | A10 | 3.3V |

| 90 | RAPI_EMMC_EN | E1 | 3.3V |

| 76 | RAPI_GPCLK1 | H5 | 3.3V |

| 45 | RAPI_GPIO12 | F10 | 3.3V |

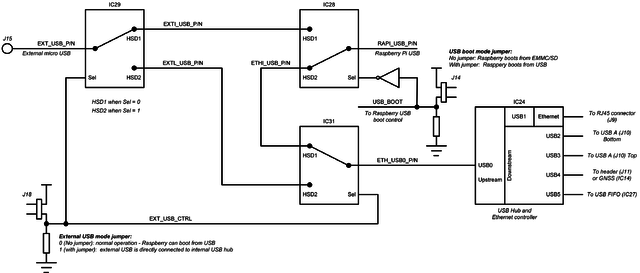

USB subsystem

LimeNet-Micro has a versatile internal USB subsystem. USB subsystem main components are Raspberry CM, switches array, configuration jumpers and connectors. USB subsystem is presented in the picture below.

Internal USB hub (IC24) has five USB ports.

| Conn. pin | Port type | Connections | Comment |

|---|---|---|---|

| USB0 | upstream | Connected to switches array and to header (J12) for debug purposes. | |

| USB1 | downstream | Internal connection to Ethernet controller | |

| USB2 | downstream | Bottom USB-A port (J10) | Can be used to connect various peripherals.

These ports (J10) is powered from same power rail and current is limited (default 0.6A total). Current limit for these ports can be changed or bypassed manually. |

| USB3 | downstream | Top USB-A port (J10) | |

| USB4 | downstream | Connected to header (J11) and via 0R resistors to GNSS (IC14) module | |

| USB5 | downstream | Directly connected to USB FIFO interface FT601 (IC27). |

There are three USB subsystem modes:

- Normal mode. Raspberry compute module USB downstream via switches is connected to internal USB hub/Ethernet controller (IC24). For this mode jumper J14 and J18 must not be mounted. Micro USB (J15) can be used only to power board depending on power jumper J27 position.

- External USB mode. Internal USB hub upstream is connected to Micro USB (J15) connector and can be connected to external host. In this case all LimeNet-Micro USB devices are visible to external system. For this mode jumper J14 must be not mounted and J18 must be mounted.

- External USB boot. Raspberry Compute module internal memory eMMC or uSD card (depending on CM model) can be updated in this mode via micro USB (J15). For this mode jumper J14 must be mounted and J18 must be not mounted. To enter USB boot mode jumpers J14 and J18 positions must be changed and power reapplied. Specific software is required to flash memory. More info [link]

USB-to-FIFO bridge

For data transfer between FPGA and USB LimeNET-Micro board has FTDI FT601 USB-to-FIFO bridge.

The controller signals description showed below:

- FT_D[31:0] - FTDI 32-bit data interface is connected to FPGA.

- FT_TXEn, FT_RXFn, FT_SIWUn, FT_WRn, FT_RDn, FT_OEn, FT_BE[3:0] - FTDI interface control signals.

- FT_CLK - FTDI interface clock. Clock from FTDI is fed to FPGA.

In the table below are listed USB controller (FTDI) pins, schematic signal name, FPGA interconnections and I/O standard.

| Chip pin (IC27) | Chip reference (IC27) | Schematic signal name | FPGA pin | I/O standard | Comment |

|---|---|---|---|---|---|

| 40 | DATA_0 | FT_D0 | A2 | 3.3V | |

| 41 | DATA_1 | FT_D1 | A3 | 3.3V | |

| 42 | DATA_2 | FT_D2 | A4 | 3.3V | |

| 43 | DATA_3 | FT_D3 | A5 | 3.3V | |

| 44 | DATA_4 | FT_D4 | A6 | 3.3V | |

| 45 | DATA_5 | FT_D5 | A7 | 3.3V | |

| 46 | DATA_6 | FT_D6 | A8 | 3.3V | |

| 47 | DATA_7 | FT_D7 | A9 | 3.3V | |

| 50 | DATA_8 | FT_D8 | A12 | 3.3V | |

| 51 | DATA_9 | FT_D9 | B13 | 3.3V | |

| 52 | DATA_10 | FT_D10 | C13 | 3.3V | |

| 53 | DATA_11 | FT_D11 | B2 | 3.3V | |

| 54 | DATA_12 | FT_D12 | B3 | 3.3V | |

| 55 | DATA_13 | FT_D13 | B4 | 3.3V | |

| 56 | DATA_14 | FT_D14 | B5 | 3.3V | |

| 57 | DATA_15 | FT_D15 | B6 | 3.3V | |

| 60 | DATA_16 | FT_D16 | D9 | 3.3V | |

| 61 | DATA_17 | FT_D17 | E6 | 3.3V | |

| 62 | DATA_18 | FT_D18 | E8 | 3.3V | |

| 63 | DATA_19 | FT_D19 | F9 | 3.3V | |

| 64 | DATA_20 | FT_D20 | E9 | 3.3V | |

| 65 | DATA_21 | FT_D21 | E10 | 3.3V | |

| 66 | DATA_22 | FT_D22 | F8 | 3.3V | |

| 67 | DATA_23 | FT_D23 | B11 | 3.3V | |

| 69 | DATA_24 | FT_D24 | B12 | 3.3V | |

| 70 | DATA_25 | FT_D25 | C11 | 3.3V | |

| 71 | DATA_26 | FT_D26 | C12 | 3.3V | |

| 72 | DATA_27 | FT_D27 | F12 | 3.3V | |

| 73 | DATA_28 | FT_D28 | G13 | 3.3V | |

| 74 | DATA_29 | FT_D29 | H13 | 3.3V | |

| 75 | DATA_30 | FT_D30 | J13 | 3.3V | |

| 76 | DATA_31 | FT_D31 | L13 | 3.3V | |

| 58 | CLK | FT_CLK | G9 | 3.3V | |

| 4 | BE_0 | FT_BE0 | H9 | 3.3V | |

| 5 | BE_1 | FT_BE1 | G12 | 3.3V | |

| 6 | BE_2 | FT_BE2 | H8 | 3.3V | |

| 7 | BE_3 | FT_BE3 | K11 | 3.3V | |

| 8 | TXE_N | FT_TXEn | J12 | 3.3V | |

| 9 | RXF_N | FT_RXFn | K12 | 3.3V | |

| 10 | SIWU_N | FT_SIWUn | - | 3.3V | 10k pull up |

| 11 | WR_N | FT_WRn | E12 | 3.3V | |

| 12 | RD_N | FT_RDn | D12 | 3.3V | |

| 13 | OE_N | FT_OEn | J9 | 3.3V | |

| 15 | RESET_N | FT_RESETn | - | - | 10k pull up, connected to shift register |

| 16 | WAKEP_N | FT_WAKEUPn | H10 | 3.3V | 10k pull up |

USB hub + Ethernet

Microchip LAN9514 IC connects all LimeNET-Micro USB periphery and in same time works as Ethernet Controller. For connection details see Table 8 and Table 9.

| Chip pin (IC24) | Chip reference (IC24) | Schematic signal name | FPGA pin | I/O standard | Comment |

|---|---|---|---|---|---|

| 20 | NFDX_LED/GPIO0 | ETH_GPIO0 | J10 | 1.8V | |

| 21 | NLNKA_LED/GPIO1 | ETH_GPIO1 | D8 | 1.8V | |

| 22 | NSPD_LED/GPIO2 | ETH_GPIO2 | L12 | 1.8V | |

| 41 | AUTOMDIX_EN | ETH_AUTOMDIX_EN | - | - | Connected to shift register |

| 12 | NRESET | ETH_NRESET | - | - | Connected to shift register |

| Connector pin | Schematic signal name | FPGA pin | I/O standard | Comment |

|---|---|---|---|---|

| P7 | ETH_LED1 | - | - | Connected to shift register |

| P13 | ETH_LED2 | - | - | Connected to shift register |

GNSS module

GNSS module can be used not only for positioning applications but for frequency measuring and tuning applications also. It provides 1PPS time synchronization pulse which is connected to FPGA.

| Chip pin (IC14) | Chip reference (IC14) | Schematic signal name | FPGA pin | I/O standard | Comment |

|---|---|---|---|---|---|

| 3 | TIMEPULSE | GNSS_TPULSE | J10 | 3.3V | |

| 20 | UART_TX/SPI_MISO | GNSS_UART_TX | D8 | 3.3V | Also connected to CM3 |

| 21 | UART_RX/SPI_MOSI | GNSS_UART_RX | L12 | 3.3V | Also connected to CM3 |

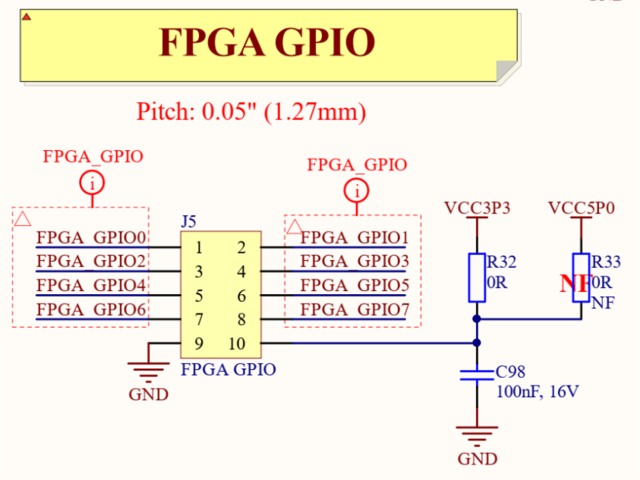

GPIO

There are eight general purpose input/output pins from FPGA connected to FPGA GPIO header (J5). Schematic names and pin connections can be found in Table 11.

| Connector pin | Schematic signal name | FPGA pin | I/O standard | Comment |

|---|---|---|---|---|

| 1 | FPGA_GPIO0 | L1 | 3.3V | |

| 2 | FPGA_GPIO1 | M7 | 3.3V | |

| 3 | FPGA_GPIO2 | N8 | 3.3V | |

| 4 | FPGA_GPIO3 | J6 | 3.3V | |

| 5 | FPGA_GPIO4 | D11 | 3.3V | |

| 6 | FPGA_GPIO5 | J7 | 3.3V | |

| 7 | FPGA_GPIO6 | A11 | 3.3V | |

| 8 | FPGA_GPIO7 | J8 | 3.3V | |

| 9 | GND | - | ||

| 10 | VCC | - | 3.3V or 5V selectable power rail. |

Voltage for pin 10 of J12 connector can be 3.3V (default) or 5V. To connect this pin to 5V power rail remove R47 and solder R48 resistors (see Figure 7).

Indication LEDs

LimeNET-Micro board comes with six dual color (red and green (RG)) indication LEDs. Most of LEDs are connected to FPGA and their function can be changed. Default LEDs functions and other information are listed in the table below.

| Board Reference | Schematic name | Board label | FPGA pin | Description |

|---|---|---|---|---|

| LED1 | FPGA_LED1_G | LED1 | - | Connected to shift register. |

| FPGA_LED1_R | - | |||

| LED2 | FPGA_LED2_G | LED2 | - | Connected to shift register. |

| FPGA_LED2_R | - | |||

| LED3 | FPGA_LED3_G | LED3 | - | Connected to shift register. |

| FPGA_LED3_R | - | |||

| LED4 | FPGA_LED4_G | LED4 | - | Connected to shift register. |

| FPGA_LED4_R | - | |||

| LED5 | FPGA_LED5_G | LED5 | - | Connected to shift register. |

| FPGA_LED5_R | - | |||

| LED6 | LED6

VCC3P3 |

- | Green LED indicates VCC3P3 power rail presence.

Red LED is unused | |

| - |

Buzzer and push button

There is one push button and buzzer connected to FPGA. Default functions and connection information are listed in the table below.

| Board Reference | Schematic name | FPGA pin | I/O standard | Description |

|---|---|---|---|---|

| LS1 | BUZZER | D13 | 3.3V | |

| SB1 | FPGA_BTN | H3 | 3.3V |

Communication interfaces (I2C, UART, SPI)

LimeNET-Micro board has various options of communication interfaces. There are I2C, UART and SPI interfaces for controlling onboard periphery. For graphical representation see Figure 8 and detailed description can be found in Table 14.

UART interface of GNSS receiver is connected to FPGA and GNSS_UART_TX line is connected to RAPI_UART1_RX through 0R resistor R56 (fitted by default). To connect RAPI_UART1_TX to GNSS_UART_RX line 0R resistor R54 has to be fitted (not fitted by default).

FPGA_I2C interface master can be either FPGA or CM3 module. By default, FPGA_I2C is connected to RAPI_I2C1. In order to connect it to RAPI_I2C0 lines 0R resistors R126, R132 has to be fitted and R130, R134 removed.

| Schematic signal name | FPGA pin | I/O standard | Comment |

|---|---|---|---|

| FPGA_I2C | |||

| FPGA_I2C_SCL | K10 | 3.3V | Serial Clock |

| FPGA_I2C_SDA | B10 | 3.3V | Data |

| FPGA_SPI | |||

| FPGA_SPI_SCLK | M5 | 3.3V | Serial Clock (FPGA output) |

| FPGA_SPI_MOSI | K5 | 3.3V | Data, master output |

| FPGA_SPI_MISO | N5 | 3.3V | Data, master input |

| FPGA_SPI_LMS_SS | J5 | 3.3V | Slave select for LMS7002M |

| FPGA_SPI_FLASH_SS | - | - | Slave select for FLASH memory, connected to shift register. |

| FPGA_SPI_DAC_SS | - | - | Slave select for XO VC DAC, connected to shift register. |

| RAPI_SPI0 | |||

| RAPI_SPI0_SCLK | F13 | 3.3V | Serial clock |

| RAPI_SPI0_MOSI | M11 | 3.3V | Data, master output |

| RAPI_SPI0_MISO | K8 | 3.3V | Data, master input |

| RAPI_SPI0_CE0 | E13 | 3.3V | Slave selects |

| RAPI_SPI1 | |||

| RAPI_SPI1_SCLK | G10 | 3.3V | Serial clock |

| RAPI_SPI1_MOSI | K13 | 3.3V | Data, master output |

| RAPI_SPI1_MISO | L11 | 3.3V | Data, master input |

| RAPI_SPI1_CE0 | A10 | 3.3V | Slave selects |

| GNSS_UART | |||

| GNSS_UART_RX | L12 | 3.3V | GNSS UART receive (FPGA output) |

| GNSS_UART_TX | D8 | 3.3V | GNSS UART receive (FPGA input) |

Temperature control

LimeNET-Micro has integrated temperature sensor which can be used to monitor board temperature through I2C interface.

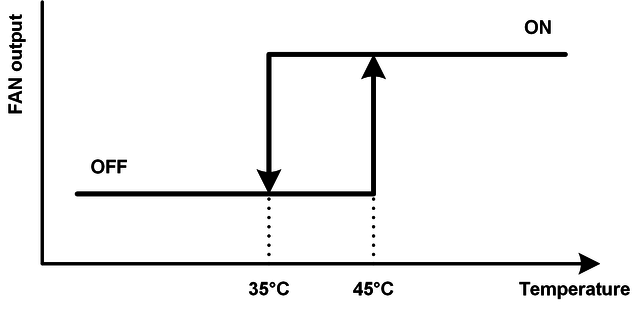

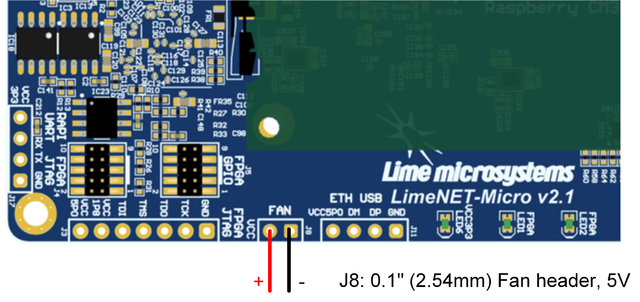

Sensor has overtemperature shutdown output connected to FPGA. Which can be used to take actions to reduce board temperature when it rises below set limits. For example, fan will be turned on if board will heat up to 45°C and FAN will be turned off if board will cool down to 35°C. Fan (5V) can be connected to J8 fan header (Figure 10).

| Schematic signal name | FPGA pin | I/O standard | Comment |

|---|---|---|---|

| FPGA_I2C_SCL | J1 | 3.3V | Serial Clock |

| FPGA_I2C_SDA | K1 | 3.3V | Data |

| LM75_OS | H1 | 3.3V | Overtemperature shutdown output (FPGA input) |

| FAN_CTLR | C5 | 3.3V | Fan control output |

Shift registers

In order to save FPGA pins LimeNET-Micro has four shift registers connected in series for controlling onboard periphery. By using 3 pins FPGA can control up to 32 outputs. For FPGA pins see Table 16 and for output description of shift register see Table 17.

| Schematic signal name | FPGA pin | I/O standard | Comment |

|---|---|---|---|

| SR_DIN | B7 | 3.3V | Serial data (connected to first shift register IC15) |

| SR_SCLK | B9 | 3.3V | Shift register clock (connected to all four shift registers – IC15, IC17, IC19, IC22) |

| SR_LATCH | D6 | 3.3V | Shift register storage clock (connected to all four shift registers – IC15, IC17, IC19, IC22) |

| Shift reg. output | Schematic signal name | Comment |

|---|---|---|

| 0 | FPGA_LED1_R | FPGA LED control |

| 1 | FPGA_LED1_G | |

| 2 | FPGA_LED2_R | |

| 3 | FPGA_LED2_G | |

| 4 | FPGA_LED3_R | |

| 5 | FPGA_LED3_G | |

| 6 | FPGA_LED4_R | |

| 7 | FPGA_LED4_G | |

| 8 | FPGA_LED5_R | |

| 9 | FPGA_LED5_G | |

| 10 | ETH_LED1 | RJ45 Ethernet connector LED control |

| 11 | ETH_LED2 | |

| 12 | LMS_RESET | LMS7002M IC1 control |

| 13 | LMS_CORE_LDO_EN | |

| 14 | LMS_RXEN | |

| 15 | LMS_TXEN | |

| 16 | FPGA_SPI_ADF_SS | FPGA_SPI slave select control |

| 17 | FPGA_SPI_DAC_SS | |

| 18 | FPGA_SPI_FLASH_SS | |

| 19 | ETH_AUTOMDIX_EN | Ethernet IC24 control |

| 20 | ETH_NRESET | |

| 21 | FT_RESETn | USB FIFO IC27 control |

| 22 | RAPI_RUN | |

| 23 | - | |

| 24 | RFSW_TX_V1 | |

| 25 | RFSW_TX_V2 | |

| 26 | RFSW_TXO_V1 | |

| 27 | RFSW_TRXA_V1 | |

| 28 | RFSW_TRXB_V1 | |

| 29 | RFSW_RXI_V1 | |

| 30 | RFSW_RX_V1 | |

| 31 | RFSW_RX_V2 |

Clock Distribution

LimeNET-Micro board has onboard VCOCXO and VCTCXO oscillators fitted. There is an option to select 30.72MHz or 40.0MHz oscillator as a reference clock for LMS7002M IC. Clock distribution block diagram is presented in Figure 11.

Oscillator frequency can be tuned by DAC (IC35 or IC37). Also, there is an option to lock oscillator frequency to external reference clock by using phase detector (IC36).

| Source | Schematic signal name | I/O standard | FPGA pin | Description |

|---|---|---|---|---|

| Clock buffer (IC34) | ||||

| RxPLL_CLK | 3.3V | - | Connected to LMS7002M | |

| TxPLL_CLK | - | Connected to LMS7002M | ||

| LMK_CLK | 3.3V | H6 | ||

| REF_CLK_OUT | 3.3V | - | Connected to J24 SMA connector | |

| REF_ADF | 3.3V | - | Connected to IC36 | |

| RF transceiver (IC1) | LMS_MCLK1 | 3.3V | G5 | |

| LMS_FCLK1 | 3.3V | L3 | ||

| LMS_MCLK2 | 3.3V | H4 | ||

| LMS_FCLK2 | 3.3V | R29 | ||

| GNSS module IC14 | GNSS_TPULSE | 3.3V | J10 | 1PPS time pulse output |

| USB FIFO IC27 | FT_CLK | 3.3V | G9 | 100MHz USB FIFO clock |

| CM3 J13 | RAPI_GPCLK1 | 3.3V | H5 | Configurable clock output from CM3 |

Clock buffer source selection:

- Clock oscillator - remove R166, R168, R169 resistors and fit one of the R162, R171, R174 resistors (depends on VCOCXO/VCTCXO selection). This is default board configuration;

- Raspberry PI (RAPI_GPCLK2) - remove R162, R171, R174 resistors and fit R166 resistor.

- J25 SMA connector (REF_CLK_IN) - remove R162, R171, R174 resistors and fit R168 resistor.

- USB hub (ETH_CLK24) - remove R162, R171, R174 resistors and fit R169 resistor.

Clock oscillator selection:

- XO1 (30.72MHz) – remove R166, R168, R169, R172, R173 and fit R162, R163 resistors. This is default board configuration.

- XO2/XO3 (30.72Mhz) – fit only one of the oscillators because they share same footprint, remove R162, R163, R166, R168, R169, R173 and fit R171, R172 resistors. By default, XO2 is fitted.

- XO4 (40MHz) - remove R162, R163, R166, R168, R169, R171, R172 and fit R174, R175 resistors.

Getting Started with LimeNET-Micro

Basic setup

To get LimeNET-Micro board up and running:

- Set “Power selection” jumper J27 to “A” position (pins 5-6, 5V micro USB power selection);

- Connect mouse and keyboard to J10 USB connectors;

- Connect monitor cable to J19 HDMI connector;

- Insert CM3 module into J13 socket (or CM3(L) module into J13 and uSD card into J16 slot).

- Connect power adapter (5V, 2A-3A) to micro USB connector J15.

FPGA programming

Intel MAX10 FPGA can be programmed using JTAG adapter such as [Intel FPGA USB Download Cable] (formerly known as Altera USB-Blaster download cable). LimeNET-Micro board has two different size and pin count JTAG headers (J4 - 10pin 0.05” pitch header and J3 - 7pin 0.1” pitch edge connector). Additional cable adapter is needed to connect download cable to LimeNET-Micro board because Intel FPGA USB Download Cable comes with 10-pin, 0.1” pitch female connector.

Board status

LimeNET-Micro board has six dual color (red/green) LED indicators fitted on top and two green indicators on Ethernet (J9) connector. Each LED except power status LED is controlled from FPGA and their function can be changed. Default LED function and their other information are listed in the table below.

| Board Reference | Schematic name | Board label | Type | Description |

|---|---|---|---|---|

| LED1 | FPGA_LED1_G | FPGA

LED1 |

CPU activity | CM3, USB FIFO and NIOS CPU activity:

Green - CM3 activity; Red - USB and NIOS CPU activity. |

| FPGA_LED1_R | ||||

| LED2 | FPGA_LED2_G | FPGA

LED2 |

Ethernet/Wi-Fi activity | Ethernet/Wi-Fi activity:

Green - Ethernet Link Activity; Red - Wi-Fi module activity. |

| FPGA_LED2_R | ||||

| LED3 | FPGA_LED3_G | FPGA

LED3 |

Clock status | Blinking indicates presence of TCXO clock.

Color indicates status of FPGA PLLs that are used for LMS digital interface clocking: Green – both PLLs are locked; Red/Green – PLL is not locked. |

| FPGA_LED3_R | ||||

| LED4 | FPGA_LED4_G | FPGA

LED4 |

TCXO control mode | No light – TCXO is controlled from DAC

Red – TCXO is controlled from phase detector and is not locked to external reference clock Green – TCXO is controlled from phase detector and is locked to external reference clock. Red and green at same time – TCXO is controlled from DAC, and its value tuned by PPS signal coming from GPS module. |

| FPGA_LED4_R | ||||

| LED5 | FPGA_LED5_G | FPGA

LED5 |

TCXO tune state | GNSS lock and VCOCXO tune state: Solid RED – no GPS lock;

Blinking RED – GPS is locked, 1s lowest accuracy tune state; Blinking RED/GREEN - GPS is locked, 10s accuracy tune state; Blinking GREEN - GPS is locked, 100s highest accuracy tune state |

| FPGA_LED5_R | ||||

| LED6 | - | VCC3P3

LED6 |

Power status | Green LED indicates VCC3P3 power rail presence. Red LED is unused |

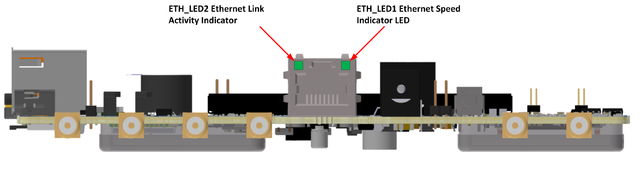

| J9 | ETH_LED1 | - | Ethernet Speed

Indicator LED |

LED is on when the Ethernet operating speed is 100 Mbs. |

| J9 | ETH_LED2 | - | Ethernet Link

Activity Indicator LED |

LED is on when a valid link is detected and blinking indicates activity. |