LimeSDR-PCIe: Difference between revisions

Jump to navigation

Jump to search

| Line 63: | Line 63: | ||

== Board Design Files == | == Board Design Files == | ||

Here are links to the schematic, PCB project and BOM | Here are links to the schematic, PCB project and BOM. | ||

'''LimeSDR-PCIe v1.2''': | |||

* LimeSDR-PCIe v1.3 [https://github.com/myriadrf/LimeSDR-PCIe/tree/master/hardware/1v3/EDA PCB project (Altium project)] | * [https://github.com/myriadrf/LimeSDR-PCIe/blob/master/hardware/1v2/EDA/Project%20Outputs%20for%20LimeSDR-PCIe_1v2/LimeSDR-PCIe_1v2_schematic_r2.PDF Schematic (PDF)] | ||

* | * [https://github.com/myriadrf/LimeSDR-PCIe/tree/master/hardware/1v2/EDA PCB project (Altium project)] | ||

* [https://github.com/myriadrf/LimeSDR-PCIe/blob/master/hardware/1v2/EDA/Project%20Outputs%20for%20LimeSDR-PCIe_1v2/BOM/LimeSDR-PCIe_1v2_BOMr2.xls BOM (XLS)] | |||

'''LimeSDR-PCIe v1.3''': | |||

* [https://github.com/myriadrf/LimeSDR-PCIe/blob/master/hardware/1v3/EDA/Project%20Outputs%20for%20LimeSDR-PCIe_1v3/LimeSDR-PCIe_1v3_schematic_r0.PDF Schematic (PDF)] | |||

* [https://github.com/myriadrf/LimeSDR-PCIe/tree/master/hardware/1v3/EDA PCB project (Altium project)] | |||

* [https://github.com/myriadrf/LimeSDR-PCIe/blob/master/hardware/1v3/EDA/Project%20Outputs%20for%20LimeSDR-PCIe_1v3/BOM/LimeSDR-PCIe_1v3_BOMr2.xls BOM (XLS)] | |||

== Additional Components == | == Additional Components == | ||

Revision as of 14:29, 28 February 2018

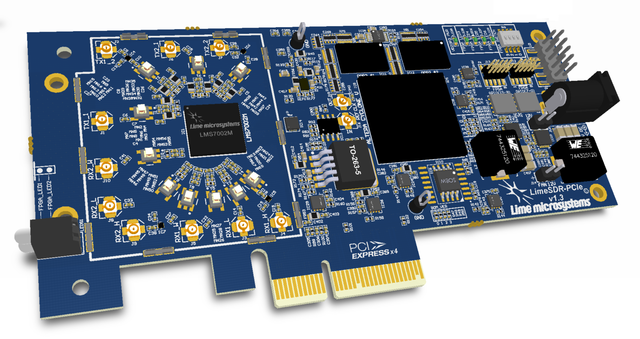

LimeSDR-PCIe Boards

Features and Specifications

| Feature | Description |

|---|---|

| RF Transceiver | Lime Microsystems LMS7002M MIMO FPRF |

| FPGA | Cyclone IV GX (EP4CGX30CF23C7N) |

| PCI Express | x4 (4 lanes) |

| Oscillator | Rakon @ 30.72MHz |

| Continuous frequency range | 100 kHz – 3.8 GHz |

| Bandwidth | 61.44MHz |

| RF connection | 10 U.FL connectors (6 RX, 4 TX) |

| Power Output (CW) | Up to 10dBm |

| Multiplexing | 2×2 MIMO |

| Power Supply | Via PCIe connector or optional external power supply |

| Status indicators | Programmable LEDs |

| Dimensions | 68,9mm x 136,85mm |

Getting Help

If you have questions, the MyriadRF Discourse is a best place to ask for help.

Documentation

- LimeSDR-PCIe v1.2 hardware description

- LimeSDR-PCIe v1.3 hardware description

- LimeSDR-PCIe driver installation description

- LimeSDR-PCIe FPGA programming

- Getting Started with LimeSDR-USB and LimeSuiteGUI - Using LimeSDR-USB board with LimeSuiteGUI software

- LimeSDR-USB Quick Test - How to check if LimeSDR-USB is working correctly

- LMS7002M (Mask 1) Transceiver Calibration - LMS7002Mr3 calibration guide, using internal MCU

- LimeSDR Made Simple - Demystifying using SDR in the real world and programming a simple example with confidence, through bite sized chunks.

- LMS7002M Datasheet (PDF) - LMS7002M RF transceiver datasheet

- LMS7002M Programming and Calibration Guide (PDF) - LMS7002M programming and calibration guide

Software

FPGA Binary

Here are the link to FPGA gateware (bitstream):

- LimeSDR-PCIe v1.2 gateware project

- LimeSDR-PCIe v1.3 gateware project

Board Design Files

Here are links to the schematic, PCB project and BOM.

LimeSDR-PCIe v1.2:

LimeSDR-PCIe v1.3:

Additional Components

Here is a list of additional components to be used with LimeSDR-PCIe board.

| |||||||||||||||||||||